Foxconn Inferno Katana English Manual. - Page 54

► Memory Remap Feature, ► Fast MRC, ► Configure DRAM Timing by SPD, ► DRAM Command Rate, ► DRAM

|

View all Foxconn Inferno Katana manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 54 highlights

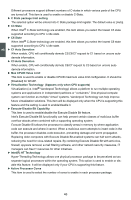

Memory Timing Config CMOS Setup Utility - Copyright (C) 1985-2009, American Megatrends, Inc. Memory Timing Config PCI MMIO ALLocation: 4GB To 3328MB Help Item Memory Remap Feature Enabled Fast MRC Disabled Enabled: ALLow Configure DRAM Timing by SPD Auto remapping of DRAM Command Rate Auto over lapped PCI memory DRAM Margin Ranks Disabled above the total physical memory. Disabled: Do not allow remapping of memory. 3 Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults ► Memory Remap Feature This item is used to enable/disable memory remapping around memory hole. PCI doesn't actually care much which addresses are used, but by convention the PC platform puts them at the top of the 32-bit address space. For many years it wasn't possible or practical to put that much RAM into a PC. But now it is, so it's up to the memory controller and host bridge to figure out what to do. Many systems cause that high RAM to simply be ignored, resulting in the loss of effective RAM. More complex systems will take the RAM that would occupy that 3.5-4GB address space and re-map it into the 4.0-4.5 address space. The RAM doesn't care because it's just an array of storage cells, it's up to the memory controller to as- sociate addresses with those storage cells. Of course, that only works if you're using a 64-bit (or 32bit physical address extension (PAE) enabled) OS that can deal with physical addresses larger than 32 bits. Once this option is enabled, BIOS will display the true size of memory installed. ► Fast MRC [Enabled]: While cold booting, MRC directly restores memory data from valid NVRAM without hardware training. [Disabled]: The cold booting with memory detection and hardware training. ► Configure DRAM Timing by SPD This item is used to select the provision of DRAM timing by SPD device. The Serial Presence Detect (SPD) device is a small EEPROM chip, mounted on a memory module. It contains important information about the module's speed, size, addressing mode and various other pa- rameters, so that the motherboard memory controller (chipset) can better access the memory. ► DRAM Command Rate This item allows you to select a delay time (in clock cycles) between sending the last data from a write operation to the memory and issuing a read command. ► DRAM Margin Ranks This item is used to get all DRAM ranks best margin. 47