Intel E5310 Specification Update

Intel E5310 - Xeon 1.6 GHz 8M L2 Cache 1066MHz FSB LGA771 Active Quad-Core Processor Manual

|

UPC - 735858190800

View all Intel E5310 manuals

Add to My Manuals

Save this manual to your list of manuals |

Intel E5310 manual content summary:

- Intel E5310 | Specification Update - Page 1

Intel® Xeon® Processor 5300 Series Specification Update December 2010 Order Number: 315338-020 Notice: The Intel® Xeon® Processor 5300 Series may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are - Intel E5310 | Specification Update - Page 2

. Performance will vary depending on the specific hardware and software used. Not available on Intel® Core™ i5-750. For more information including details on which processors support HT Technology, visit http://www.intel.com/info/hyperthreading 64-bit Intel® Xeon® processors with Intel®64 requires - Intel E5310 | Specification Update - Page 3

Contents Contents Revision History ...4 Preface ...5 Summary Tables of Changes 7 Identification Information 17 Errata ...19 Specification Changes 53 Specification Clarifications 54 Documentation Changes 55 Intel® Xeon® Processor 5300 Series 3 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 4

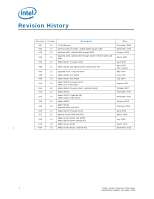

Added AJ94 through AJ100. Deleted AJ82 and AJ84. Added AJ101 through AJ103. -006 1.0 Added AJ104 and Specification Clarification AJ1 -007 -008 -009 -010 -011 -012 -013 -014 -015 -016 -017 - 2009 March 2010 December 2010 4 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 5

consolidated into the specification update and are no longer published in other documents. This document may also contain information that was not previously published. Affected Documents Document Title Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Document Number/ Location 315569 Note - Intel E5310 | Specification Update - Page 6

request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so forth). 6 Intel® Xeon® Processor 5300 - Intel E5310 | Specification Update - Page 7

in Intel's microprocessor Specification Updates: Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium®D processor Intel® Xeon® processor 5000 series 64-bit Intel® Xeon - Intel E5310 | Specification Update - Page 8

Mobile Intel® Celeron® processor Intel® Pentium® 4 processor Intel® Xeon® processor MP Intel ® Xeon® processor Mobile Intel® Pentium® 4 processor supporting Intel® Hyper-Threading Technology on 90-nm process technology Intel® Pentium® 4 processor on 90 nm process 64-bit Intel® Xeon® processor with - Intel E5310 | Specification Update - Page 9

AK = Intel® Core™2 Extreme quad-core processor QX6000? sequence and Intel® Core™2 Quad processor Q6000 sequence AL = Intel® Xeon® processor 7100 series AM = Intel® Celeron® processor 400 sequence AN = Intel® Pentium® dual-core processor AO = Intel® Xeon® processor 3200 series AP = Intel® Xeon® - Intel E5310 | Specification Update - Page 10

Incorrect LER MSRs May be Incorrectly Updated Performance Monitoring Events for Retired Instructions (C0H) May Not Be Accurate Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification Using 2M/4M Pages When A20M - Intel E5310 | Specification Update - Page 11

May Result in Unpredictable Behavior Performance Monitor IDLE_DURING_DIV (18h) Count May Not be Accurate Values for LBR/BTS/BTM will be Incorrect after an Exit from SMM ShutdownCondition May Disable Non-Bootstrap Processors Intel® Xeon® Processor 5300 Series 11 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 12

MCE During a Far Transfer May Corrupt ESP In Single-Stepping on Branches Mode, the BS Bit in the PendingDebug-Exceptions Field of the Guest State Area will be Incorrectly Set by VM-Exit on a MOV to CR8 Instruction 12 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 13

as a Result of VIP/VIF Check on SYSEXIT and SYSRET Performance Monitoring Event SIMD_UOP_TYPE_EXEC.MUL is Counted Incorrectly for PMULUDQ Instruction Storage of PEBS Record Delayed Following Execution of MOV SS or STI Intel® Xeon® Processor 5300 Series 13 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 14

Cause a Triple Fault Shutdown IA32_MC1_STATUS MSR Bit[60] Does Not Reflect Machine Check Error Reporting Enable Correctly A VM Exit Due to a Fault While Delivering a Software Interrupt May Save Incorrect Data into the VMCS 14 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 15

Calculated After an FP Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode A 64-bit Register IP-relative Instruction May Return Unexpected Results Specification Changes Number SPECIFICATION CHANGES AJ1 Implementation of System Management Range Registers - Intel E5310 | Specification Update - Page 16

© '05 x53XX (FPO) Table 1. LAOTTPONO S/N The Quad-Core Intel® Xeon® Processor 5300 Series stepping can be identified by the following component markings: Intel® Xeon® Processor 5300 Series Identification Information (Sheet 1 of 2) Processor S-Spec Number Core Stepping CPUID Core Freq (GHz - Intel E5310 | Specification Update - Page 17

8. These parts have Execute Disable bit functionality. 9. These parts have Intel® Virtualization Technology (Intel® VT) enabled. 10. This is a Intel® Xeon® Processor 5300 Series with a 40W TDP (Thermal Design Power) Intel® Xeon® Processor 5300 Series 17 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 18

SIMD instruction retired. Regardless of DR7 programming, if the linear address of a retiring memory store MOVD/MOVQ/MOVNTQ instruction executed matches the address in DR3, the CFH counter may be incorrectly incremented. 18 Intel® Xeon® Processor 5300 Series Specification Update, December - Intel E5310 | Specification Update - Page 19

invalid TSS fault instead of a #GP fault. Intel has not observed this erratum with any commercially available software. Workaround: None Identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series 19 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 20

PMH_PAGE_WALK is used to count the number of page walks resulting from Data Translation Look-Aside Buffer (DTLB) and Instruction Translation Look-Aside (ITLB) misses. Under certain conditions, this counter may be incorrect. 20 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 21

of Changes. AJ16. Performance Monitoring Event For Number Of Reference Cycles When The Processor Is Not Halted (3CH) Does Not Count According To The Specification Problem: The CPU_CLK_UNHALTED performance monitor with mask 1 counts bus clock cycles instead of counting the core clock cycles at - Intel E5310 | Specification Update - Page 22

in Incorrect Address Translations Problem: An external A20M# pin if enabled forces address bit 20 to be masked instructions is one or two instructions after the floating-point operation which causes the precision exception: • FST m32real 22 Intel® Xeon® Processor 5300 Series Specification - Intel E5310 | Specification Update - Page 23

a "sticky" bit, i.e., once . Problem: processor may transfer control to an unintended address. The result of fetching code at that address is unpredictable and may include an unexpected trap or fault, or execution of the instructions found there. Intel® Xeon® Processor 5300 Series 23 Specification - Intel E5310 | Specification Update - Page 24

to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field Problem: Processors supporting Intel® Virtualization Technology (Intel® VT) can execute VMCALL from within the Virtual Machine Monitor (VMM) to activate dual-monitor treatment of SMIs and - Intel E5310 | Specification Update - Page 25

support Execute Disable Bit functionality. Implication: Writing to IA32_MISC_ENABLE [34] bit is silently ignored without generating a fault. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series 25 Specification - Intel E5310 | Specification Update - Page 26

system bus master, writing data into a currently executing code segment of a second processor with the intent of having the second processor execute that data as code is called cross-modifying code (XMC). XMC that does not 26 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 27

: Do not use locked stores that span cache lines in the monitored address range. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series 27 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 28

AJ37. REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 Problem: REP CMPS (Compare String) and SCAS (Scan String) instructions in 64-bit mode may terminate before the count in RCX reaches zero if the initial value of RCX is greater than or equal to 0X100000000. - Intel E5310 | Specification Update - Page 29

processor is in 64-bit mode. • The last floating point operation was in compatibility mode • Bit 31 of the FPU Data (Operand) Pointer is set. • An FXSAVE instruction 3 above mentioned debug support facilities are used. Intel® Xeon® Processor 5300 Series 29 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 30

Virtual-8086 (VM86) Problem: Following a task switch to any fault handler that was initiated while the processor was in VM86 mode, if there is an additional fault while servicing the original task switch then the VM bit . 30 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 31

SMI was triggered by an instruction that read from an I/O port. The SMM handler must not restart an I/O instruction if the platform has not been configured to generate a synchronous SMI for the recorded I/O port address. Intel® Xeon® Processor 5300 Series 31 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 32

Behavior Problem: Updating a page table entry by changing R/W, U/S or P bits without TLB shootdown (as defined by the 4 step procedure in "Propagation of Page Table and Page Directory Entry Changes to Multiple Processors" in volume 3A of the IA-32 Intel® Architecture Software Developer's Manual - Intel E5310 | Specification Update - Page 33

Data Size or Lead to Memory-Ordering Violations Problem: Under certain conditions as described in the Software Developers Manual section "Outof-Order Stores For String Operations in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or REP STOS as fast strings - Intel E5310 | Specification Update - Page 34

reaches an invalid temperature the CPU does not generate a Thermal interrupt even if a programmed threshold is crossed. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 34 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 35

Status Will Not be Indicated Unless IA32_DEBUGCTL[12] is Set IA32_PERF_GLOBAL_STATUS MSR (38EH) bit [62] when set, indicates that a PEBS (Precise Event-Based Sampling) overflow has occurred and a PMI (Performance Monitor Intel® Xeon® Processor 5300 Series 35 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 36

to CR8 Instruction Problem: In a system supporting Intel® Virtualization Technology, the BS bit (bit 14 of the Pending-Debug-Exceptions field) in the guest state area will be incorrectly set when all of the following conditions occur: • The processor is running in VMX non-root as a 64 bit mode - Intel E5310 | Specification Update - Page 37

. Performance Monitor SSE Retired Instructions May Return Incorrect Values Problem: The SIMD_INST_RETIRED (Event: C7H) is used to track retired SSE instructions. Due to this erratum, the processor may inaccurately count certain types of instructions resulting in values higher than the number of - Intel E5310 | Specification Update - Page 38

Instruction from CR8 Register with 16 Bit Operand Size Will Leave Bits 63:16 of the Destination Register Unmodified Problem: Moves to/from control registers are supposed to ignore REW.W and the 66H (operand size) prefix. In systems supporting Intel® Virtualization Technology, when the processor - Intel E5310 | Specification Update - Page 39

Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3: System Programming Guide. Status: For the steppings affected, see the Summary Tables of Changes. AJ86. Unaligned Accesses to Paging Structures May Cause the Processor to Hang Problem: When an unaligned access is performed - Intel E5310 | Specification Update - Page 40

unexpectedly due to invalid instructions. Intel has not observed this erratum with any commercially available software. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 40 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 41

. Problem: Storage of PEBS Record Delayed Following Execution of MOV SS or STI When a performance monitoring counter is configured for PEBS (Precise Event Based Sampling), overflow of the counter results in storage of a PEBS record in the PEBS Intel® Xeon® Processor 5300 Series 41 Specification - Intel E5310 | Specification Update - Page 42

linear address has an A (Accessed) bit that is clear • One of the following simultaneous exception conditions is present following the code transition - Code #DB and code #PF - Code Segment Limit Violation #GP and code #PF 42 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 43

may over count. The extent of over counting depends on the number of memory accesses retiring while the counter is active. Workaround: None identified Status: For the steppings affected, see the Summary Tables of Changes. Intel® Xeon® Processor 5300 Series 43 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 44

few branches before the PEBS sample that triggered the PMI. Workaround: None Identified. Status: For the steppings affected, see the Summary Tables of Changes. 44 Intel® Xeon® Processor 5300 Series Specification Update, December 2010 - Intel E5310 | Specification Update - Page 45

2] of IA32_FIXED_CTR_CTRL MSR • Only the G-step processor will support threshold-based error status (IA32_MCG_CAP [bit 11] = 1) Only the G-step processor will support thresholdbased error status (IA32_MCG_CAP [bit 11] = 1) Intel® Xeon® Processor 5300 Series 45 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 46

May Not Count Some Transitions Problem: Performance Monitor Event FP_MMX_TRANS_TO_MMX (Event CCH, Umask 01H) counts transitions from x87 Floating Point (FP) to MMX™ instructions. Due to this erratum, if only a small number of MMX instructions (including EMMS) are executed immediately - Intel E5310 | Specification Update - Page 47

FXSAVE May Lead to Memory-Ordering Violations Problem: Under certain conditions, as described in the Software Developers Manual section "Outof-Order Stores For String Operations in Pentium 4, Intel Xeon, and P6 Family Processors", the processor may perform REP MOVS or REP STOS as write combining - Intel E5310 | Specification Update - Page 48

Clear RF Problem: RF (Resume Flag), bit 16 of the EFLAGS/RFLAGS register, is used to restart instruction execution without getting an instruction breakpoint on the instruction following a debug breakpoint exception. Due to this erratum, in a system supporting Intel® Virtualization Technology, when - Intel E5310 | Specification Update - Page 49

of Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide. Status: For the steppings affected, see the Summary Tables of Changes. AJ123. Problem: returns from SMM with the "IA- Intel® Xeon® Processor 5300 Series 49 Specification Update, December 2010 - Intel E5310 | Specification Update - Page 50

64-bit operating system which may run code accessing 32-bit addresses, care must be taken to ensure that no 80-bit FP accesses are wrapped around a 4-Gbyte boundary. Status: For the steppings affected, see the Summary Table of Changes. 50 Intel® Xeon® Processor 5300 Series Specification Update - Intel E5310 | Specification Update - Page 51

AJ127. A 64-bit Register IP-relative Instruction May Return Unexpected Results Problem: Under an unlikely and complex sequence of conditions in 64-bit mode, a register IPrelative instruction result may be incorrect. Implication: A register IP-relative instruction result may be incorrect and - Intel E5310 | Specification Update - Page 52

: • Quad-Core Intel® Xeon® Processor 5300 Series Datasheet Implementation of System Management Range Registers This processor has implemented SMRRs (System Management Range Registers). SMRRs are defined in Section 10.11.2.4 of the Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume - Intel E5310 | Specification Update - Page 53

Clarifications The Specification Clarifications listed in this section apply to the following documents: • Quad-Core Intel® Xeon® Processor 5300 Series Datasheet • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide AJ1. Clarification of - Intel E5310 | Specification Update - Page 54

the following documents: Quad-Core Intel® Xeon® Processor 5300 Series Datasheet All Documentation Changes will be incorporated into a future version of the appropriate Processor documentation. Note: Documentation changes for Intel® 64 and IA-32 Architecture Software Developer's Manual volumes 1, 2A - Intel E5310 | Specification Update - Page 55

Intel® Xeon® Processor 5300 Series 55 Specification Update, December 2010

Order Number: 315338-020

Notice:

The Intel® Xeon® Processor 5300 Series may contain design defects or errors known as errata which

may cause the product to deviate from published specifications. Current characterized errata are available on

request.

Intel® Xeon® Processor 5300 Series

Specification Update

December 2010