Intel D925XHY D925XHY Technical Product Specification - Page 49

PCI Conventional Interrupt Routing Map

|

View all Intel D925XHY manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 49 highlights

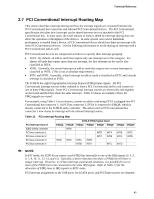

Technical Reference 2.7 PCI Conventional Interrupt Routing Map This section describes interrupt sharing and how the interrupt signals are connected between the PCI Conventional bus connectors and onboard PCI Conventional devices. The PCI Conventional specification describes how interrupts can be shared between devices attached to the PCI Conventional bus. In most cases, the small amount of latency added by interrupt sharing does not affect the operation or throughput of the devices. In some special cases where maximum performance is needed from a device, a PCI Conventional device should not share an interrupt with other PCI Conventional devices. Use the following information to avoid sharing an interrupt with a PCI Conventional add-in card. PCI Conventional devices are categorized as follows to specify their interrupt grouping: • INTA: By default, all add-in cards that require only one interrupt are in this category. For almost all cards that require more than one interrupt, the first interrupt on the card is also classified as INTA. • INTB: Generally, the second interrupt on add-in cards that require two or more interrupts is classified as INTB. (This is not an absolute requirement.) • INTC and INTD: Generally, a third interrupt on add-in cards is classified as INTC and a fourth interrupt is classified as INTD. The ICH6-R has eight Programmable Interrupt Request (PIRQ) input signals. All PCI Conventional interrupt sources either onboard or from a PCI Conventional add-in card connect to one of these PIRQ signals. Some PCI Conventional interrupt sources are electrically tied together on the board and therefore share the same interrupt. Table 13 shows an example of how the PIRQ signals are routed. For example, using Table 13 as a reference, assume an add-in card using INTA is plugged into PCI Conventional bus connector 3. In PCI bus connector 3, INTA is connected to PIRQB, which is already connected to the ICH6-R audio controller. The add-in card in PCI Conventional bus connector 3 now shares an interrupt with the onboard interrupt source. Table 13. PCI Interrupt Routing Map PCI Interrupt Source IEEE-1394a controller PCI bus connector 1 PCI bus connector 2 PCI bus connector 3 PCI bus connector 4 PIRQA PIRQB INTA INTD INTC ICH6-R PIRQ Signal Name PIRQC PIRQD PIRQE PIRQF INTA INTB INTB INTA INTD INTC INTA INTB INTC PIRQG INTB INTA INTD PIRQH INTC INTD NOTE In PIC mode, the ICH6-R can connect each PIRQ line internally to one of the IRQ signals (3, 4, 5, 6, 7, 9, 10, 11, 12, 14, and 15). Typically, a device that does not share a PIRQ line will have a unique interrupt. However, in certain interrupt-constrained situations, it is possible for two or more of the PIRQ lines to be connected to the same IRQ signal. Refer to Table 12 for the allocation of PIRQ lines to IRQ signals in APIC mode. PCI interrupt assignments to the USB ports, Serial ATA ports, and PCI Express ports are dynamic. 49