MSI K9NU User Guide - Page 42

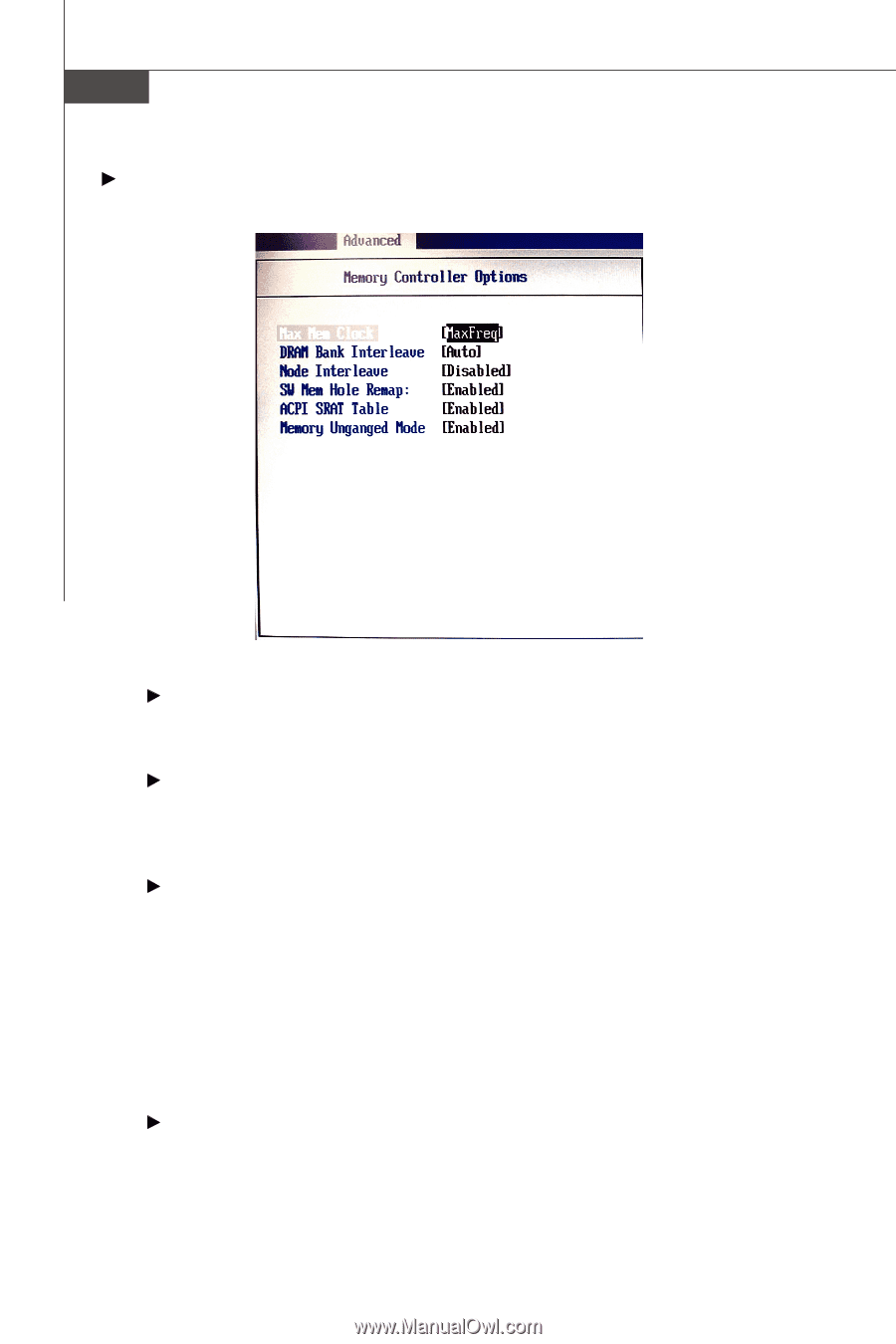

MS-9655 Server Board, Memory Controller Options, Max Mem Clock, DRAM Bank Interleave, Node

|

View all MSI K9NU manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

MS-9655 Server BoardB Memory Controller Options Max Mem Clock Use this field to configure the highest clock frequency of the installed DRAM. Users may also assign a lower memory clock frequency here. DRAM Bank Interleave Interleaved memory is system memory divided into two or more sections. Setting to [Enabled] allows memory to be accessed faster since each section of memory is capable of being utilized at once. Node Interleave AMD Opteron CPU supports a mode called node interleave. W hen node interleave is disabled, the memory controller maps the local memory of each processor to a single contiguous range of physical addresses. This allows the operating system to map user data to local memory, whenever possible, to allow programs to access data the most rapidly. W hen node interleave is enabled, physical addresses are partitioned into 4KB blocks, and alternated among the processors. The operating system is then unable to use NUMA optimizations, and the memory space is treated as if the system were an SMP system. SW M em Hole Remap This setting enables the software to remap the physical memory to an address higher than 4GB. 3-8