Toshiba Tecra M2-S410 Maintenance Manual - Page 24

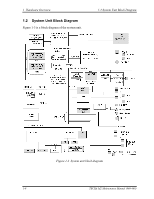

Hardware Overview, 2 System Unit Block Diagram

|

View all Toshiba Tecra M2-S410 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

1 Hardware Overview 1.2 System Unit Block Diagram ‰ Intel ICH4-M (South Bridge) • One Intel FW82801DBM is used. • This gate array has the following features: - Hub Link Interface - PCI Rev2.2 Interface (6 PCI REQ/GNT Pairs) - BusMaster IDE Controller (Ultra ATA 100/66/33) - USB 1.1/2.0 Controller 6 Ports (EHCI: Enhanced Host Controller) - I/O APIC (ACPI 1.0b) - SMBus2.0 Controller - FWH Interface (BIOS) - LPC Interface (EC/KBC, Super I/O) - IRQ Controller - Serial Interrupt Controller - Power Management Controller - Deeper Sleep (C4) Support - Suspend/Resume Control - AC'97 2.2 Interface - Internal RTC - Internal LAN Controller (WfM2.0) - 421-ball 31×31mm BGA Package ‰ PC Card Controller Gate Array • One YEBISU3S gate array is used. • This gate array has the following functions and components. - PCI interface (PCI Rev. 2.2) - CardBus/PC Card controller (Yenta2 Ver. 2.2) - SD memory card controller (SDHC Ver. 1.2) - SD IO card controller (Ver. 1.0) - SmartMedia controller (SMHC Ver.01/SMIL1.0) (not used in this computer) - SIO (UART) controller (MS Debug Port Specification Ver. 1.0) - Docking station interface (Q-SW control, reset control) - External device interface 1-10 TECRA M2 Maintenance Manual (960-468)