Foxconn A7GM-S English Manual. - Page 42

► Twrrd Write to Read DIMM Termination Turn-around. Optional only if CPU supports

|

View all Foxconn A7GM-S manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

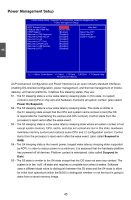

3 ► tRP (Precharge Command Period) This item allows you to select the row precharge time (in clock cycles). ► tRTP (Internal Read to Precharge Command Delay) Internal READ Command to PRECHARGE Command delay ► tRAS (Active-to-Precharge Delay) This item allows you to set the minimum RAS# active time (in clock cycles). ► tRC (Active-to-Active/Auto-Refresh Command Period) This item allows you to set the row cycle time (in clock cycles). tRC = tRAS + tRP. ► tWR (Write Recovery) This item allows you to select the write recovery time (in clock cycles). ► tRRD (Active-to-Active of a Different Bank) This item allows you to select a delay time (in clock cycles) between the RAS# and RAS# strobe signals. ► TrwtTO (Read-to-Write Turnaround for Data. Optional only if CPU supports) This timing parameter ensures read-to-write data-bus turnaround. ► Twrrd (Write to Read DIMM Termination Turn-around. Optional only if CPU supports) This timing parameter accounts for termination timing when a write is followed by a read to a different DIMM. ► tWTR (Internal Write to Read Command Delay) This item allows you to select a delay time (in clock cycles) between sending the last data from a write operation to the memory and issuing a read command. ► Twrwr (Write to Write Timing. Optional only if CPU supports) This timing parameter accounts for turn-around timing when a write is followed by a write to a different DIMM. ► Trdrd (Read to Read Timing. Optional only if CPU supports) This timing parameter accounts for turn-around and termination timing when a read is followed by a read to a different chip select. ► tRFC0, 1, 2, 3 (Auto-Refresh-to-Active/Auto-Refresh Command Period) Refresh to Refresh or Refresh to Active command interval. Trfc3: auto-refresh row cycle time for logical DIMM 3 Trfc2: auto-refresh row cycle time for logical DIMM 2 Trfc1: auto-refresh row cycle time for logical DIMM 1 Trfc0: auto-refresh row cycle time for logical DIMM 0 35