Intel BLKDH61WWB3 Product Specification - Page 18

Memory Configurations

|

View all Intel BLKDH61WWB3 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 18 highlights

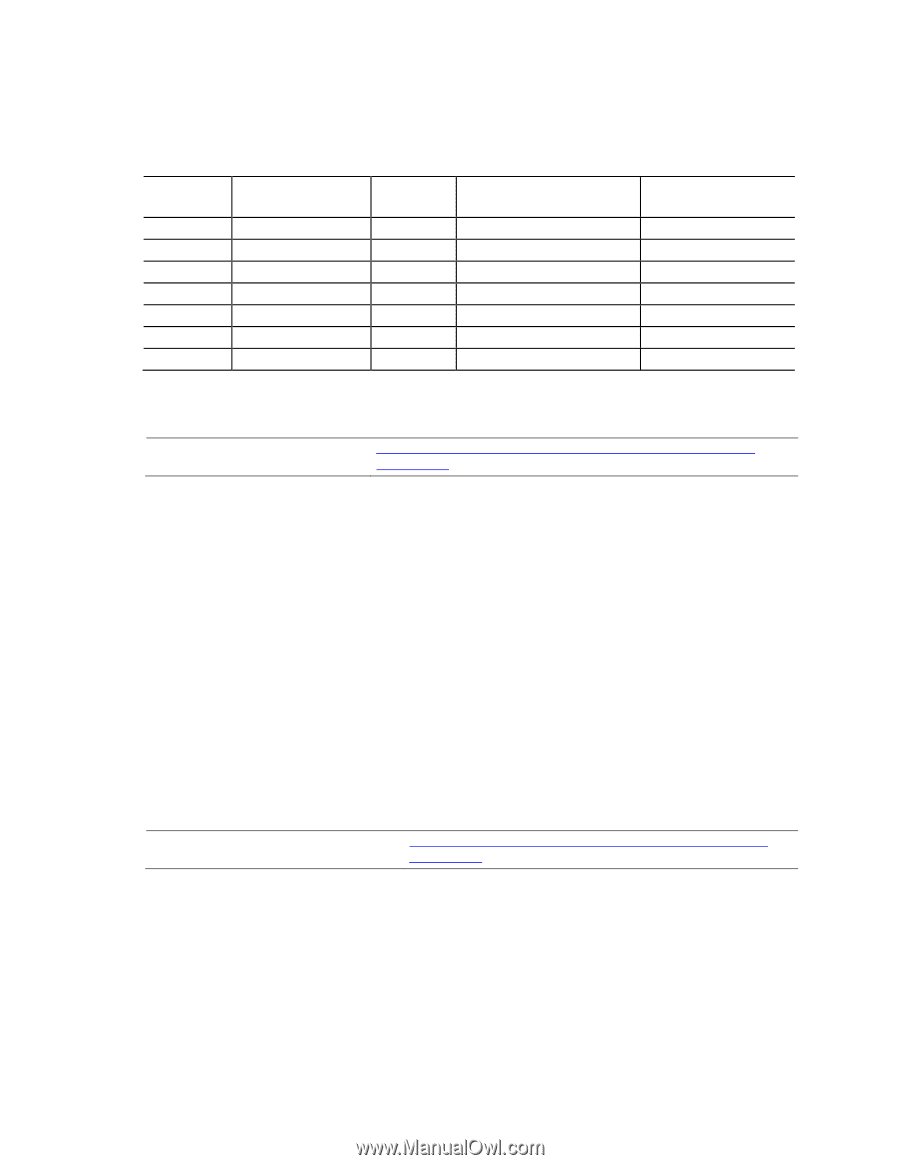

Intel Desktop Board DH61WW Technical Product Specification Table 3 lists the supported DIMM configurations. Table 3. Supported Memory Configurations DIMM Capacity Configuration (Note) SDRAM Density SDRAM Organization Front-side/Back-side Number of SDRAM Devices 512 MB SS 1024 MB SS 1 Gbit 64 M x16/empty 4 1 Gbit 128 M x8/empty 8 1024 MB SS 2048 MB DS 2 Gbit 128 M x16/empty 4 1 Gbit 128 M x8/128 M x8 16 2048 MB SS 2 Gbit 128 M x16/empty 8 4096 MB DS 2 Gbit 256 M x8/256 M x8 16 4096 MB SS 4 Gbit 512 M x8/empty 8 Note: "DS" refers to double-sided memory modules (containing two rows of SDRAM) and "SS" refers to single-sided memory modules (containing one row of SDRAM). For information about... Tested Memory Refer to: http://support.intel.com/support/motherboards/desktop/sb/CS025414.htm 1.6.1 Memory Configurations The Intel Core i7, Intel Core i5, Intel Core i3, and Intel Pentium processors support the following types of memory organization: • Dual channel (Interleaved) mode. This mode offers the highest throughput for real world applications. Dual channel mode is enabled when the installed memory capacities of both DIMM channels are equal. Technology and device width can vary from one channel to the other but the installed memory capacity for each channel must be equal. If different speed DIMMs are used between channels, the slowest memory timing will be used. • Single channel (Asymmetric) mode. This mode is equivalent to single channel bandwidth operation for real world applications. This mode is used when only a single DIMM is installed or the memory capacities are unequal. Technology and device width can vary from one channel to the other. If different speed DIMMs are used between channels, the slowest memory timing will be used. For information about... Memory Configuration examples Refer to: http://www.intel.com/support/motherboards/desktop/sb/cs011965.htm 18