Intel E6320 Specification Update

Intel E6320 - Core 2 Duo Dual-Core Processor Manual

|

UPC - 735858192576

View all Intel E6320 manuals

Add to My Manuals

Save this manual to your list of manuals |

Intel E6320 manual content summary:

- Intel E6320 | Specification Update - Page 1

2nd Generation Intel® Core™ Processor Family Desktop, Intel® Pentium® Processor Family Desktop, and Intel® Celeron® Processor Family Desktop Specification Update June 2013 Notice: Products may contain design defects or errors known as errata which may cause the product to deviate from - Intel E6320 | Specification Update - Page 2

instructions marked "reserved" or "undefined". Intel Intel® Core™ i5750. For more information including details on which processors support Intel® HT Technology, visit http://www.intel.com/info/hyperthreading. For Enhanced Intel SpeedStep® Technology, see the Processor Spec Finder at http://ark.intel - Intel E6320 | Specification Update - Page 3

Contents Revision History ...5 Preface ...7 Summary Tables of Changes 9 Identification Information 16 Errata ...23 Specification Changes 65 Specification Clarifications 66 Documentation Changes 67 § § Specification Update 3 - Intel E6320 | Specification Update - Page 4

4 Specification Update - Intel E6320 | Specification Update - Page 5

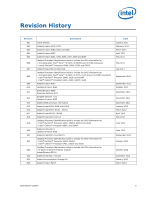

Identification table to include the SKU information for - 2nd Generation Intel® Core™ i5-2320, i3-2125, i3-2130 and i3-2120T processors - Intel® Pentium® Processor G860, G630 and G630T - Intel® Celeron® Processor G540, G530, G530T, G440 Added Erratum BJ95 Updated Erratum BJ65 Added Erratum BJ96 - Intel E6320 | Specification Update - Page 6

Revision -027 -028 -029 Added Erratum BJ122 Added SKUs Added Errata BJ123-BJ125 Added Errata BJ126-BJ128 Description § § Date April 2013 May 2013 June 2013 6 Specification Update - Intel E6320 | Specification Update - Page 7

Document Title AP-485, Intel® Processor Identification and the CPUID Instruction Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference Manual A-M Intel® 64 and IA - Intel E6320 | Specification Update - Page 8

as, core speed, L2 cache size, package type, etc. as described in the processor identification information table. Read all notes associated with each S-Spec number. to the appropriate product specification or user documentation (datasheets, manuals, etc.). § § 8 Specification Update - Intel E6320 | Specification Update - Page 9

Tables of Changes The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the processor. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through - Intel E6320 | Specification Update - Page 10

to MemoryOrdering Violations Code Segment Limit/Canonical Faults on RSM May be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address Onto From Pending PEBS During SMM General Protection Fault (#GP) for Instructions Greater than 15 Bytes May be Preempted #GP on Segment - Intel E6320 | Specification Update - Page 11

STI The Processor May Report a #TS Instead of a #GP Fault VM Exits Due to "NMI-Window Exiting" May Be Delayed by One Instruction Pending x87 From the Intel® VT-d Remap Engine Fault Not Reported When Setting Reserved Bits of Intel® VT-d Queued Invalidation Descriptors VPHMINPOSUW Instruction in Vex - Intel E6320 | Specification Update - Page 12

Supported Performance-Counter Overflow Indication May Cause Undesired Behavior XSAVE Executed During Paging-Structure Modification May Cause Unexpected Processor Processor May Fail to Acknowledge a TLP Request Executing The GETSEC Instruction While Throttling May Result in a Processor Intel® - Intel E6320 | Specification Update - Page 13

May Result in Unexpected Behavior Intel® Trusted Execution Technology ACM Revocation Mapped I/O or Uncached Memory May Cause The Logical Processor to Hang PEBS May Unexpectedly Signal a PMI After or Out of STM Performance Monitor Precise Instruction Retired Event May Present Wrong Indications The - Intel E6320 | Specification Update - Page 14

Not Ignored with VCVT*2SI Instructions MCI_ADDR May be Incorrect For Cache Parity Errors Instruction Fetches Page-Table Walks May Not Updated After a UC Error is Logged Spurious Intel® VT-d Interrupts May Occur When the PFO Bit is Set Processor May Livelock During On Demand Clock Modulation The - Intel E6320 | Specification Update - Page 15

Documentation Changes Number DOCUMENTATION CHANGES BJ1 On-Demand Clock Modulation Feature Clarification § § Specification Update 15 - Intel E6320 | Specification Update - Page 16

:8], to indicate whether the processor belongs to the Intel386, Intel486, Pentium, Pentium Pro, Pentium 4, or Intel® Core™ processor family. 2. The Extended register after RESET, bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model - Intel E6320 | Specification Update - Page 17

10 BRAND PROC# SLxxx SPEED [COO] [FPO] e4 LOT NO S/N Table 1. Processor Identification (Sheet 1 of 3) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Processor Graphics Frequency SR00C i7-2600K D-2 000206a7h 3.4 / 1333 / 850 SR00B i7-2600 - Intel E6320 | Specification Update - Page 18

Identification (Sheet 2 of 3) S-Spec Number Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Processor Graphics Frequency SR009 i5-2500S D-2 000206a7h 2.7 / 1333 / 850 SR00A i5-2500T D-2 000206a7h 2.3 / 1333 / 650 SR00Q i5-2400 D-2 000206a7h - Intel E6320 | Specification Update - Page 19

Processor Number Stepping Processor Signature Core Frequency (GHz) / DDR3 (MHz) / Processor Graphics Frequency SR05Y SR060 SR057 SR0MF SR058 SR05Q SR05P SR059 SR066 SR05S SR05U SR05R SR05T SR0GR SR0BY SR061 SR05L SR05H SR05K SR05J SR0RS SR0S0 SR0S8 SR05V SR0RZ SR05M SR05N SR059 i3-2120 i3 - Intel E6320 | Specification Update - Page 20

SS Instruction if it is Followed by an Instruction That Signals a Floating Point Exception Problem: A MOV SS/POP SS instruction should software or system. Workaround: As recommended in the IA32 Intel® Architecture Software Developer's Manual, the use of MOV SS/POP SS in conjunction with - Intel E6320 | Specification Update - Page 21

a floating point instruction directly after a MOV SS or POP SS instruction. Status: For Memory ordering may be violated. Intel has not observed this erratum Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address Onto the Stack Problem: Normally, when the processor - Intel E6320 | Specification Update - Page 22

first far JMP. Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3A: System Programming Guide, Part 1, in the All Breakpoints Matched When a MOV/POP SS is Followed by a Store or an MMX Instruction Problem: Normally, data breakpoints matches that occur on a MOV SS, r/m or POP SS - Intel E6320 | Specification Update - Page 23

Changes. BJ11. Fault on ENTER Instruction May Result in Unexpected Values on Stack Frame Problem: The ENTER instruction is used to create a procedure IA-32 Intel® Architecture Software Developer's Manual, Vol. 1, Basic Architecture, for information on the usage of the ENTER instructions. This - Intel E6320 | Specification Update - Page 24

. Status: For the steppings affected, see the Summary Tables of Changes. BJ14. General Protection Fault (#GP) for Instructions Greater than 15 Bytes May be Preempted Problem: When the processor encounters an instruction that is greater than 15 bytes in length, a #GP is signaled when the - Intel E6320 | Specification Update - Page 25

the SMI was triggered by an instruction that read from an I/O port. The SMM handler must not restart an I/O instruction if the platform has not been Tables of Changes. BJ18. LER MSRs May Be Unreliable Problem: Due to certain internal processor events, updates to the LER (Last Exception Record) - Intel E6320 | Specification Update - Page 26

in Hang Problem: If the target linear address range for a MONITOR or CLFLUSH is mapped to the local xAPIC's address space, the processor will hang. Implication: When this erratum occurs, the processor will hang. The local xAPIC's address space must be uncached. The MONITOR instruction only - Intel E6320 | Specification Update - Page 27

of Changes. BJ24. Performance Monitoring Event FP_MMX_TRANS_TO_MMX May Not Count Some Transitions Problem: Performance Monitor Event FP_MMX_TRANS_TO_MMX (Event CCH, Umask 01H) counts transitions from x87 Floating Point (FP) to MMX™ instructions. Due to this erratum, if only a small number of MMX - Intel E6320 | Specification Update - Page 28

Manual section "Out- of-Order Stores For String Operations in Pentium 4, Intel Xeon, and P6 Family Processors" the processor performs REP MOVS or REP STOS as fast strings. Due to this erratum fast string REP MOVS/REP STOS instructions Pending May Be Mishandled Problem: In certain circumstances, - Intel E6320 | Specification Update - Page 29

) May be Signaled Earlier Than Expected Problem: x87 instructions that trigger #MF normally service interrupts before the #MF. Due to this erratum, if an instruction that triggers #MF is executed while Enhanced Intel SpeedStep® Technology transitions, Intel® Turbo Boost Technology transitions, or - Intel E6320 | Specification Update - Page 30

Complete with an Incorrect Byte Count Problem: PCIe* Upstream IO and Configuration accesses are not supported. If an IO or Configuration request set to the same byte count as the offending request. Implication: The processor response to an unsupported PCIe access may not fully comply to the PCIe - Intel E6320 | Specification Update - Page 31

a lower than expected speed. Intel has not observed this erratum Instructions May Return Incorrect Values Problem: Performance Monitoring counter SIMD_INST_RETIRED (Event: C7H) is used to track retired SSE instructions. Due to this erratum, the processor may also count other types of instructions - Intel E6320 | Specification Update - Page 32

Problem: The FP (Floating Point) Data Operand Pointer is the effective address of the operand associated with the last non-control FP instruction executed by the processor in this way is not a normal programming practice. Intel has not observed this erratum with any commercially available software - Intel E6320 | Specification Update - Page 33

to reserved bits of Intel VT-d Queued Invalidation Descriptors. Workaround: None identified Status: For the steppings affected, see the Summary Tables of Changes. BJ42. VPHMINPOSUW Instruction in Vex Format Does Not Signal #UD When vex.vvvv !=1111b Problem: Processor does not signal #UD - Intel E6320 | Specification Update - Page 34

BJ44. Problem: VMREAD/VMWRITE Instruction May Not Fail When Accessing an Unsupported Field in VMCS The Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B states that execution of VMREAD or VMWRITE should fail if the value of the instruction's register source operand - Intel E6320 | Specification Update - Page 35

Intel 64 and IA-32 Intel® Architecture Software Developer's Manual, Volume 3A, in the section titled Programming the PAT. Intel L0s Enabled and Link Retrain Performed Problem: If the Processor PCI Express* root port is executions of the VZEROALL and VZEROUPPER instructions in 64-bit mode to ensure - Intel E6320 | Specification Update - Page 36

Physical Memory Ranges May Cause a System Hang Problem: Processor Graphics internal message cycles occurring concurrently with a in the VEX.mmmmm field. Implication: Due to this erratum, some undefined instruction encodings may produce a #NM instead of a #UD exception. Workaround: Software - Intel E6320 | Specification Update - Page 37

a Processor Hang Problem: If the processor throttles, due to either high temperature thermal conditions or due to an explicit operating system throttling request (TT1), while executing GETSEC[SENTER] or GETSEC[SEXIT] instructions, then under certain circumstances, the processor may hang. Intel has - Intel E6320 | Specification Update - Page 38

this erratum, the processor may hang without reporting errors when receiving a malformed PCIe transaction. Intel has not observed as Being Supported Problem: LTR (Latency Tolerance Reporting) is a new optional feature specified in PCIe rev. 2.1. The processor reports LTR as supported in LTRS - Intel E6320 | Specification Update - Page 39

While typical exit latencies are not impacted, the worst case core C-state exit latency may be over twice the value specified in the Intel® 64 and IA-32 Architectures Optimization Reference Manual and may lead to a delay in servicing interrupts. Intel has not observed any system failures due to this - Intel E6320 | Specification Update - Page 40

Link Speed May Not Change From 5.0 GT/s to 2.5 GT/s Problem: If a PCI Express device changes its supported PCIe link speed from 5.0 GT/s to 2.5 GT/ s speed to 2.5 GT/s. Implication: Intel has not observed any PCI Express device that changes supported link speed without actually initiating a - Intel E6320 | Specification Update - Page 41

Structure Changes to Multiple Processors" of Volume 3A of IA-32 Intel® Architecture Software Developer's Manual, for recommendations for TCfgWr May Cause Unpredictable System Behavior Problem: TCfgWr (Trusted Configuration Writes) is a PCIe Base spec deprecated transaction type which should be - Intel E6320 | Specification Update - Page 42

. BJ69. Executing The GETSEC Instruction While Throttling May Result in a Processor Hang Problem: If the processor throttles, due to either high instructions, then under certain circumstances, the processor may hang. Implication: Possible hang during execution of GETSEC instruction. Intel - Intel E6320 | Specification Update - Page 43

Tables of Changes. BJ75. #GP May be Signaled When Invalid VEX Prefix Precedes Conditional Branch Instructions Problem: When a 2-byte opcode of a conditional branch (opcodes 0F8xH, for any value of x) instruction resides in 16-bit code-segment and is associated with invalid VEX prefix, it may - Intel E6320 | Specification Update - Page 44

management state entry until render reset occurs. Any asynchronous Intel VT-d (Virtualization Technology for Directed I/O) access to During Package Power States May Cause a System Hang Problem: Under a complex set of internal conditions when the processor is in a deep power state (package C3, - Intel E6320 | Specification Update - Page 45

the steppings affected, see the Summary Tables of Changes. BJ84. Display Corruption May be Seen After Graphics Voltage Rail (VCC_AXG) Power Up Problem: Powering up the processor graphics logic in the cases of initial poweron or Sx resume state power up may cause a nondeterministic state in the - Intel E6320 | Specification Update - Page 46

Registers Problem: In 64-bit mode, using REX.W=1 with PCMPESTRI and PCMPESTRM or VEX.W=1 with VPCMPESTRI and VPCMPESTRM should support a VMLAUNCH May Not Update The Launch State of the VMCS Problem: Successful VM entries using the VMLAUNCH instruction should set the launch state of the VMCS to - Intel E6320 | Specification Update - Page 47

this case, the load by the later instruction may cause a page fault that indicates that translation for the page. Intel has not observed this erratum Credits May Cause a System Hang Problem: Under certain conditions, if a : Under certain conditions, the processor may encounter a Posted Data - Intel E6320 | Specification Update - Page 48

core's net value. Status: For the steppings affected, see the Summary Tables of Changes. BJ92. PDIR May Not Function Properly With FREEZE_PERFMON_ON_PMI Problem: When the PDIR (Precise Distribution for Instructions incorrect PEBS events or invalid processor state. Workaround: A software - Intel E6320 | Specification Update - Page 49

Zero Even Though The Package Reserves More Than One APIC ID Problem: When maximum number of addressable IDs for logical processors in this physical package (CPUID.01H.EBX[23:16]) and maximum number of addressable IDs for processor cores in the physical package, (CPUID.04H.EAX[31:26]) indicate more - Intel E6320 | Specification Update - Page 50

May Cause Unexpected PMI or PEBS Events Problem: PDIR (Precise Distribution for Instructions Retired) mechanism is activated by programming INST_RETIRED is Not Treated as an Unsupported Request Problem: The PCIe* root port does not support LTR (Latency Tolerance Reporting) capability. However - Intel E6320 | Specification Update - Page 51

Processor to Hang Problem: Under a complex set of conditions, using VMASKMOV to reference memory mapped I/O or uncached memory may cause the logical processor to hang. Implication: Due to this erratum, the logical processor may hang. Intel's Software Developers Manual the VMCALL instruction. This - Intel E6320 | Specification Update - Page 52

Retired Event May Present Wrong Indications Problem: When the PDIR (Precise Distribution for Instructions Retired) mechanism is activated (INST_RETIRED.ALL (event C0H, umask value 00H) on Counter 1 programmed in PEBS mode), the processor may return wrong PEBS/PMI interrupts and/or incorrect - Intel E6320 | Specification Update - Page 53

Changes. BJ108. Unexpected #UD on VZEROALL/VZEROUPPER Problem: Execution of the VZEROALL or VZEROUPPER instructions in 64-bit mode with VEX.W set to occur immediately after VM entry unless the VM entry put the logical processor in the wait-for SIPI state. Due to this erratum, such VM exits do - Intel E6320 | Specification Update - Page 54

for a 64-bit guest. Intel has not observed this erratum with any commercially available software. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. BJ113. VEX.L is Not Ignored with VCVT*2SI Instructions Problem: The VEX.L bit should be - Intel E6320 | Specification Update - Page 55

BJ116. Problem: Reported Maximum Memory Frequency Capability May Be Higher Than Expected The Intel® Pentium® Processor G645, Intel® Pentium® Processor G645T and Intel® Celeron® Processor G555 are specified for 1066 MT/s maximum DDR3 memory frequency, but report support for 1333 MT/s.The value in - Intel E6320 | Specification Update - Page 56

Instructions May Result in Unpredictable Graphics Controller Behavior Problem: Specific source-copy blitter instructions in Intel® HD Graphics 2000 and 3000 Processor dropped or may increment an enabled counter on the physical core's other thread rather than the thread experiencing the event. The - Intel E6320 | Specification Update - Page 57

logged. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. BJ124. Spurious Intel® VT-d Interrupts May Occur When the PFO Bit is Set Problem: When the PFO (Primary Fault Overflow) field (bit [0] in the VT-d FSTS [Fault Status] register) is set - Intel E6320 | Specification Update - Page 58

instructions with the lock prefix that either split a cacheline or access UC memory. Implication: Program execution may stall on both threads of the core Bit Paging Problem: When 32-bit paging is in use, the processor should bit paging without changing CR3. Intel has not observed this erratum with - Intel E6320 | Specification Update - Page 59

Implication: Software that uses the value reported in IA32_VMX_VMCS_ENUM[9:1] to read and write all VMCS fields may omit one field. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. § § Specification Update 59 - Intel E6320 | Specification Update - Page 60

Developer's Manual, Volume 2A: Instruction Set Reference Manual A-M • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference Manual N-Z • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide • Intel® 64 - Intel E6320 | Specification Update - Page 61

Developer's Manual, Volume 2A: Instruction Set Reference Manual A-M • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference Manual N-Z • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide • Intel® 64 - Intel E6320 | Specification Update - Page 62

Developer's Manual, Volume 2A: Instruction Set Reference Manual A-M • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference Manual N-Z • Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide • Intel® 64 - Intel E6320 | Specification Update - Page 63

Table 14-2. CPUID Signatures for Legacy Processors That Resolve to Higher Performance Setting of Conflicting Duty Cycle Requests DisplayFamily_Display Model 0F_xx 06_1F 06_2C 06_36 DisplayFamily_Display Model 06_1C 06_25 06_2E DisplayFamily_Display Model 06_1A - Intel E6320 | Specification Update - Page 64

64 Specification Update

Reference Number: 324643-029

Notice:

Products may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Current characterized errata are available on request.

2nd Generation Intel

®

Core™

Processor Family Desktop, Intel

®

Pentium

®

Processor Family

Desktop, and Intel

®

Celeron

®

Processor Family Desktop

Specification Update

June 2013