Intel E6320 Specification Update - Page 11

Errata Sheet 2 of 5, Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode

|

UPC - 735858192576

View all Intel E6320 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 11 highlights

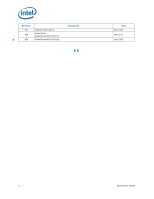

Errata (Sheet 2 of 5) Number Steppings D-2 Q-0 Status BJ26 X X No Fix BJ27 X X No Fix BJ28 X X No Fix BJ29 X X No Fix BJ30 X X No Fix BJ31 X X No Fix BJ32 X X No Fix BJ33 X X No Fix BJ34 X X No Fix BJ35 X X No Fix BJ36 X X No Fix BJ37 X X No Fix BJ38 X X No Fix BJ39 X X No Fix BJ40 X X No Fix BJ41 X X No Fix BJ42 X X No Fix BJ43 X X No Fix BJ44 X X No Fix BJ45 X X No Fix BJ46 X X No Fix BJ47 X X No Fix BJ48 X X No Fix BJ49 X X No Fix BJ50 X X No Fix BJ51 X X No Fix BJ52 X X No Fix BJ53 X X No Fix ERRATA Reported Memory Type May Not Be Used to Access the VMCS and Referenced Data Structures Single Step Interrupts with Floating Point Exception Pending May Be Mishandled Storage of PEBS Record Delayed Following Execution of MOV SS or STI The Processor May Report a #TS Instead of a #GP Fault VM Exits Due to "NMI-Window Exiting" May Be Delayed by One Instruction Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected Values for LBR/BTS/BTM Will be Incorrect after an Exit from SMM Unsupported PCIe* Upstream Access May Complete with an Incorrect Byte Count Malformed PCIe* Transactions May be Treated as Unsupported Requests Instead of as Critical Errors PCIe* Root Port May Not Initiate Link Speed Change Incorrect Address Computed For Last Byte of FXSAVE/FXRSTOR or XSAVE/ XRSTOR Image Leads to Partial Memory Update Performance Monitor SSE Retired Instructions May Return Incorrect Values FP Data Operand Pointer May Be Incorrectly Calculated After an FP Access Which Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode FP Data Operand Pointer May Be Incorrectly Calculated After an FP Access Which Wraps a 64-Kbyte Boundary in 16-Bit Code Spurious Interrupts May be Generated From the Intel® VT-d Remap Engine Fault Not Reported When Setting Reserved Bits of Intel® VT-d Queued Invalidation Descriptors VPHMINPOSUW Instruction in Vex Format Does Not Signal #UD When vex.vvvv !=1111b LBR, BTM or BTS Records May have Incorrect Branch From Information After an EIST/T-state/S-state/C1E Transition or Adaptive Thermal Throttling VMREAD/VMWRITE Instruction May Not Fail When Accessing an Unsupported Field in VMCS Clock Modulation Duty Cycle Cannot be Programmed to 6.25% Execution of VAESIMC or VAESKEYGENASSIST With An Illegal Value for VEX.vvvv May Produce a #NM Exception Memory Aliasing of Code Pages May Cause Unpredictable System Behavior PCI Express* Graphics Receiver Error Reported When Receiver With L0s Enabled and Link Retrain Performed Unexpected #UD on VZEROALL/VZEROUPPER Perfmon Event LD_BLOCKS.STORE_FORWARD May Overcount Conflict Between Processor Graphics Internal Message Cycles And Graphics Reads From Certain Physical Memory Ranges May Cause a System Hang Execution of Opcode 9BH with the VEX Opcode Extension May Produce a #NM Exception Executing The GETSEC Instruction While Throttling May Result in a Processor Hang Specification Update 11