Intel E6320 Specification Update - Page 10

Errata (Sheet 5 of 5), MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB - 64 bit

|

UPC - 735858192576

View all Intel E6320 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 10 highlights

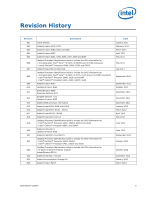

Errata (Sheet 1 of 5) Number Steppings D-2 Q-0 Status BJ1 X X No Fix BJ2 X X No Fix BJ3 X X No Fix BJ4 X X No Fix BJ5 X X No Fix BJ6 X X No Fix BJ7 X X No Fix BJ8 X X No Fix BJ9 X X No Fix BJ10 X X No Fix BJ11 X X No Fix BJ12 X X No Fix BJ13 X X No Fix BJ14 X X No Fix BJ15 X X No Fix BJ16 X X No Fix BJ17 X X No Fix BJ18 X X No Fix BJ19 X X No Fix BJ20 X X No Fix BJ21 X X No Fix BJ22 X X No Fix BJ23 X X No Fix BJ24 X X No Fix BJ25 X X No Fix ERRATA An Enabled Debug Breakpoint or Single Step Trap May Be Taken after MOV SS/ POP SS Instruction if it is Followed by an Instruction That Signals a Floating Point Exception APIC Error "Received Illegal Vector" May be Lost An Uncorrectable Error Logged in IA32_CR_MC2_STATUS May also Result in a System Hang B0-B3 Bits in DR6 For Non-Enabled Breakpoints May be Incorrectly Set Changing the Memory Type for an In-Use Page Translation May Lead to MemoryOrdering Violations Code Segment Limit/Canonical Faults on RSM May be Serviced before Higher Priority Interrupts/Exceptions and May Push the Wrong Address Onto the Stack Corruption of CS Segment Register During RSM While Transitioning From Real Mode to Protected Mode Debug Exception Flags DR6.B0-B3 Flags May be Incorrect for Disabled Breakpoints DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/POP SS is Followed by a Store or an MMX Instruction EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change Fault on ENTER Instruction May Result in Unexpected Values on Stack Frame Faulting MMX Instruction May Incorrectly Update x87 FPU Tag Word FREEZE_WHILE_SMM Does Not Prevent Event From Pending PEBS During SMM General Protection Fault (#GP) for Instructions Greater than 15 Bytes May be Preempted #GP on Segment Selector Descriptor that Straddles Canonical Boundary May Not Provide Correct Exception Error Code IO_SMI Indication in SMRAM State Save Area May be Set Incorrectly IRET under Certain Conditions May Cause an Unexpected Alignment Check Exception LER MSRs May Be Unreliable LBR, BTS, BTM May Report a Wrong Address when an Exception/Interrupt Occurs in 64-bit Mode MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error MONITOR or CLFLUSH on the Local XAPIC's Address Space Results in Hang MOV To/From Debug Registers Causes Debug Exception PEBS Record not Updated when in Probe Mode Performance Monitoring Event FP_MMX_TRANS_TO_MMX May Not Count Some Transitions REP MOVS/STOS Executing with Fast Strings Enabled and Crossing Page Boundaries with Inconsistent Memory Types may use an Incorrect Data Size or Lead to Memory-Ordering Violations 10 Specification Update