Intel P4000RP Technical Product Specification - Page 260

Intel® Server Board S1200V3RP

|

View all Intel P4000RP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 260 highlights

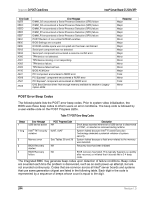

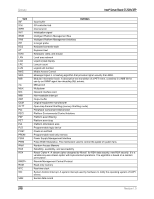

Glossary Intel® Server Board S1200V3RP Term IBF ICH IERR INIT IPMB IPMI ITP KCS KT KVM LAN LCD LPC LUN MAC MD5 MIB ms MUX NIC NMI OBF OEM OLTT PCI PECI PEF PET PIA PLD POST PROM PSMI PWM RAM RAS RC4 RMCP+ ROM RTC SCI SDR Input buffer Definition I/O controller hub Internal error Initialization signal Intelligent Platform Management Bus Intelligent Platform Management Interface In-target probe Keyboard controller style Keyboard text Keyboard, video, and mouse Local area network Liquid crystal display Low pin count Logical unit number Media Access Control Message Digest 5. A hashing algorithm that provides higher security than MD2. Modular information block. A descriptive text translation of a PET event, contained in a MIB file for use by an SNMP agent hen decoding SEL entries. Millisecond Multiplexer Network interface card Non-maskable interrupt Output buffer Original equipment manufacturer Open-loop thermal throttling (memory throttling mode) Peripheral Component Interconnect Platform Environmental Control Interface Platform event filtering Platform event trap Platform information area Programmable logic device Power-on self-test Programmable read-only memory Power Supply Management Interface Pulse Width Modulation. The mechanism used to control the speed of system fans. Random Access Memory Reliability, availability, and serviceability Rivest Cipher 4. A stream cipher designed by Rivest* for RSA data security, now RSA security. It is a variable key-size stream cipher with byte-oriented operations. The algorithm is based on a random permutation. Remote Management Control Protocol Read-only memory Real-time clock System Control Interrupt. A system interrupt used by hardware to notify the operating system of ACPI events. Sensor data record 248 Revision 1.0