Sony MZ-NF810CK Service Manual - Page 50

IC Pin Function Description

|

View all Sony MZ-NF810CK manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 50 highlights

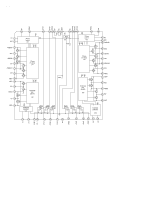

MZ-NF810/NF810CK 6-9. IC Pin Function Description • IC801 CXD2680-203GA (SYSTEM CONTROLLER, DIGITAL SIGNAL PROCESSOR) Pin No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 Pin Name OSCI OSCO VREFL AOUTL AOUTR VREFR ASYO ASYI BIAS RFI PCO FILI FILO CLTV PEAK BOTM ABCD FE VC ADIO ADRB SE TE AUX1 ADRT DCHG APC ADFG APCREF TRDR TFDR FFDR FRDR FS4 SFDR SPRD SPFD SPDV SPDW SPCU SPCV SPCW SLDV SLDW SLCU SLCV SLCW SRDR DIN DADT I/O Description I Resonator connection terminal for the system clock (22.5792MHz) O Resonator connection terminal for the system clock (22.5792MHz) O Reference voltage terminal connected to the capacitor (for the built-in D/A converter L-CH) O Built-in D/A converter L-CH signal output O Built-in D/A converter R-CH signal output O Reference voltage terminal connected to the capacitor (for the built-in D/A converter R-CH) O Playback EFM duplex signal output I Playback EFM comparator slice level input I Bias current input terminal for the playback EFM comparator I Playback EFM RF signal input from the RF amplifier O Phase comparison output terminal for the playback EFM system master PLL I Filter input terminal for the playback EFM system master PLL O Filter output terminal for the playback EFM system master PLL I Internal VCO control voltage input terminal for the playback EFM system master PLL I Peak hold signal input of the light amount signal (RF/ABCD) from the RF amplifier I Bottom hold signal input of the light amount signal (RF/ABCD) from the RF amplifier I Light amount signal (ABCD) input from the RF amplifier I Focus error signal input from the RF amplifier I Middle point voltage input from the RF amplifier O Monitor output terminal of A/D converter input signal Not used (open) I The lower limit voltage of A/D converter input terminal (connected to the ground) I Sled error signal input from the RF amplifier I Tracking error signal input from the RF amplifier I Auxiliary A/D input (fixed at "H" in this set) I The upper limit voltage of A/D converter input terminal (fixed at "H" in this set) I Connecting terminal with the analog power supply of low impedance (fixed at "H" in this set) I Error signal input for the laser automatic power control (fixed at "H" in this set) I ADIP duplex FM signal (22.05±1kHz) input from the RF amplifier O Reference PWM signal output for the laser automatic power control to the RF amplifier O Tracking servo drive PWM signal output (-) to the coil driver O Tracking servo drive PWM signal output (+) to the coil driver O Focus servo drive PWM signal output (+) to the coil driver O Focus servo drive PWM signal output (-) to the coil driver O 176.4kHz clock signal output O Sled servo drive PWM signal output to the motor driver O Spindle motor drive control signal output (U) to the motor driver O Spindle servo drive PWM signal output to the motor driver O Spindle motor drive control signal output (V) to the motor driver O Spindle motor drive control signal output (W) to the motor driver I Spindle motor drive comparison signal input (U) from the motor driver I Spindle motor drive comparison signal input (V) from the motor driver I Spindle motor drive comparison signal input (W) from the motor driver O Sled motor drive control signal output (V) to the motor driver O Sled motor drive control signal output (W) to the motor driver I Sled motor drive comparison signal input (U) from the motor driver I Sled motor drive comparison signal input (V) from the motor driver I Sled motor drive comparison signal input (W) from the motor driver O Sled motor drive control signal output (U) to the motor driver I Digital audio signal input O Audio data output terminal Not used (open) 50