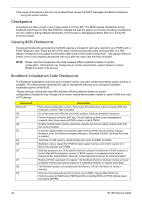

eMachines EL1852 eMachines EL1852 Service Guide - Page 52

Do R/W test to CH-2 count reg. Initialize CH-0 as system timer.Install the POSTINT1Ch

|

View all eMachines EL1852 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 52 highlights

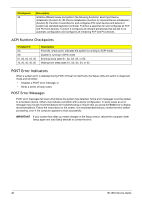

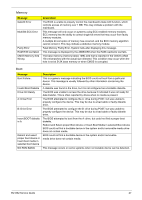

Checkpoint 06 07 08 C0 C1 C2 C5 C6 C7 0A 0B 0C 0E 13 24 30 2A 2C 2E 31 33 Description Do R/W test to CH-2 count reg. Initialize CH-0 as system timer.Install the POSTINT1Ch handler. Enable IRQ-0 in PIC for system timer interrupt. Traps INT1Ch vector to "POSTINT1ChHandlerBlock." Fixes CPU POST interface calling pointer. Initializes the CPU. The BAT test is being done on KBC. Program the keyboard controller command byte is being done after Auto detection of KB/MS using AMI KB-5. Early CPU Init Start -- Disable Cache - Init Local APIC Set up boot strap processor Information Set up boot strap processor for POST Enumerate and set up application processors Re-enable cache for boot strap processor Early CPU Init Exit Initializes the 8042 compatible Key Board Controller. Detects the presence of PS/2 mouse. Detects the presence of Keyboard in KBC port. Testing and initialization of different Input Devices. Also, update the Kernel Variables. Traps the INT09h vector, so that the POST INT09h handler gets control for IRQ1. Uncompress all available language, BIOS logo, and Silent logo modules. Early POST initialization of chipset registers. Uncompress and initialize any platform specific BIOS modules. GPNV is initialized at this checkpoint. Initialize System Management Interrupt. Initializes different devices through DIM. See DIM Code Checkpoints section for more information. Initializes different devices. Detects and initializes the video adapter installed in the system that have optional ROMs. Initializes all the output devices. Allocate memory for ADM module and uncompress it. Give control to ADM module for initialization. Initialize language and font modules for ADM. Activate ADM module. Initializes the silent boot module. Set the window for displaying text information. Checkpoint 37 38 39 3A 3B 3C 40 50 Description Displaying sign-on message, CPU information, setup key message, and any OEM specific information. Initializes different devices through DIM. See DIM Code Checkpoints section for more information. USB controllers are initialized at this point. Initializes DMAC-1 & DMAC-2. Initialize RTC date/time. Test for total memory installed in the system. Also, Check for DEL or ESC keys to limit memory test. Display total memory in the system. Mid POST initialization of chipset registers. Detect different devices (Parallel ports, serial ports, and coprocessor in CPU, ... etc.) successfully installed in the system and update the BDA, EBDA...etc. Programming the memory hole or any kind of implementation that needs an adjustment in system RAM size if needed. 44 EL1852 Service Guide