Asus M4A78T-E User Manual - Page 72

Enable Clock to All DIMMs [Disabled]

|

UPC - 610839169559

View all Asus M4A78T-E manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 72 highlights

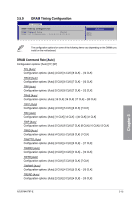

3.5.8 Memory Configuration Ai Tweaker Memory Configuration Bank Interleaving Channel Interleaving Enable Clock to All DIMMs MemClk Tristate C3/ATLVID Memory Hole Remapping DCT Unganged Mode Power Down Enable Page Smashing [Auto] [XOR of Address bit] [Disabled] [Disabled] [Enabled] [Auto] [Disabled] [Disabled] Enable Bank Memory Interleavng. Bank Interleaving [Auto] Configuration options: [Disabled] [Auto] Channel Interleaving [XOR of Address bit] Configuration options: [Disabled] [Address bits 6] [Address bits 12] [XOR of Address bits [20:16, 6]] [XOR of Address bits [20:16, 9]] Enable Clock to All DIMMs [Disabled] Enables unused clocks to DIMMs even if the memory slots are not populated. Configuration options: [Disabled] [Enabled] MemClk Tristate C3/ATLVID [Disabled] Configuration options: [Disabled] [Enabled] Memory Hole Remapping [Enabled] Configuration options: [Disabled] [Enabled] DCT Unganged Mode [Auto] Configuration options: [Auto] [Disabled] [Enabled] Power Down Enable [Disabled] Enables or disables the DDR power down mode. Configuration options: [Disabled] [Enabled] Power Down Mode [Channel] Allows you to set the DDR power down mode. This item appears only when you enable the previous item. Configuration options: [Channel] [Chip Select] Page Smashing [Disabled] S/W Control of Page Smashing Mechanism. Configuration options: [Disabled] [IC] [DC] [Both] Chapter 3 3-14 Chapter 3: BIOS setup