Intel D845HV Product Specification - Page 45

Technical Reference

|

View all Intel D845HV manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 45 highlights

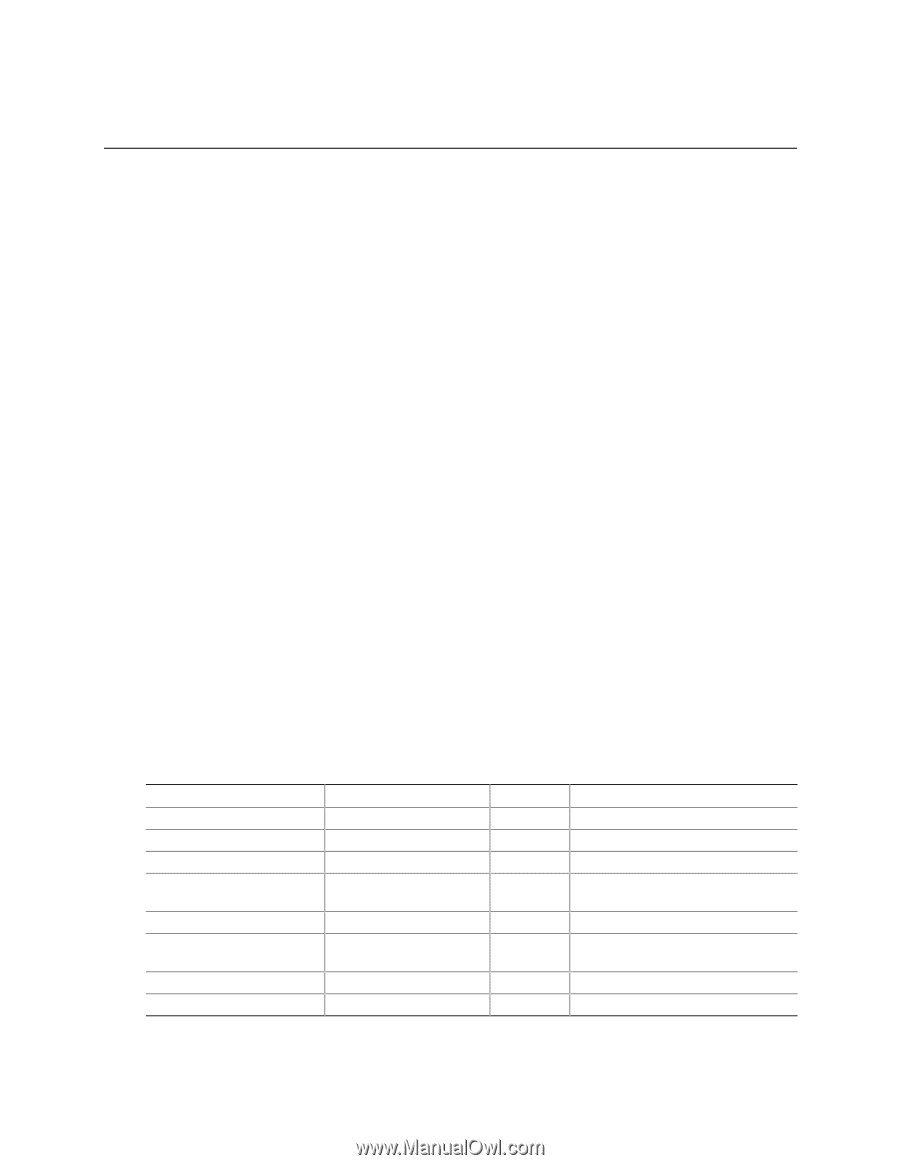

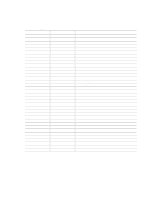

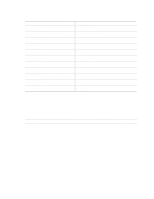

2 Technical Reference What This Chapter Contains 2.1 Introduction...45 2.2 Memory Map ...45 2.3 I/O Map ...46 2.4 DMA Channels ...48 2.5 PCI Configuration Space Map 48 2.6 Interrupts ...49 2.7 PCI Interrupt Routing Map 49 2.8 Connectors ...51 2.9 Jumper Blocks...72 2.10 Mechanical Considerations 74 2.11 Electrical Considerations 78 2.12 Thermal Considerations 81 2.13 Reliability ...83 2.14 Environmental ...83 2.15 Regulatory Compliance 84 2.1 Introduction Sections 2.2 - 2.6 contain several standalone tables. Table 12 describes the system memory map, Table 13 shows the I/O map, Table 14 lists the DMA channels, Table 15 defines the PCI configuration space map, and Table 16 describes the interrupts. The remaining sections in this chapter are introduced by text found with their respective section headings. 2.2 Memory Map Table 12. System Memory Map Address Range (decimal) 1024 K - 3145728 K 960 K - 1024 K 896 K - 960 K 800 K - 896 K Address Range (hex) 100000 - BFFFFFFF F0000 - FFFFF E0000 - EFFFF C8000 - DFFFF 640 K - 800 K 639 K - 640 K A0000 - C7FFF 9FC00 - 9FFFF 512 K - 639 K 0 K - 512 K 80000 - 9FBFF 00000 - 7FFFF Size 3071 MB 64 KB 64 KB 96 KB 160 KB 1 KB 127 KB 512 KB Description Extended memory Runtime BIOS Reserved Available high DOS memory (open to the PCI bus) Video memory and BIOS Extended BIOS data (movable by memory manager software) Extended conventional memory Conventional memory 45