Intel I3-530 Specifications - Page 10

Errata Sheet 2 of 5, EOI Transaction May Not be Sent if Software Enters Core C6 During an Interrupt - core processor

|

View all Intel I3-530 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 10 highlights

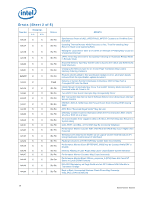

Errata (Sheet 2 of 5) Number Steppings C-2 K-0 Status AAU26 X X No Fix AAU27 X X No Fix AAU28 X X No Fix AAU29 X X No Fix AAU30 X X No Fix AAU31 X X No Fix AAU32 X X No Fix AAU33 X Fixed AAU34 X X No Fix AAU35 X X No Fix AAU36 X X No Fix AAU37 X X No Fix AAU38 X X No Fix AAU39 X X No Fix AAU40 X X No Fix AAU41 X X No Fix AAU42 X X No Fix AAU43 X X No Fix AAU44 X X No Fix AAU45 X X No Fix AAU46 X X No Fix AAU47 X X No Fix AAU48 X X No Fix AAU49 X X No Fix AAU50 X X No Fix ERRATA Synchronous Reset of IA32_APERF/IA32_MPERF Counters on Overflow Does Not Work Disabling Thermal Monitor While Processor is Hot, Then Re-enabling, May Result in Stuck Core Operating Ratio Writing the Local Vector Table (LVT) when an Interrupt is Pending May Cause an Unexpected Interrupt xAPIC Timer May Decrement Too Quickly Following an Automatic Reload While in Periodic Mode Reported Memory Type May Not Be Used to Access the VMCS and Referenced Data Structures Changing the Memory Type for an In-Use Page Translation May Lead to Memory-Ordering Violations Erratum AAU32 added to this specification Update in error; all erratum details removed from the specification update document. Delivery of Certain Events Immediately Following a VM Exit May Push a Corrupted RIP onto the Stack Infinite Stream of Interrupts May Occur if an ExtINT Delivery Mode Interrupt is Received while All Cores in C6 Two xAPIC Timer Event Interrupts May Unexpectedly Occur EOI Transaction May Not be Sent if Software Enters Core C6 During an Interrupt Service Routine FREEZE_WHILE_SMM Does Not Prevent Event From Pending PEBS During SMM APIC Error "Received Illegal Vector" May be Lost DR6 May Contain Incorrect Information When the First Instruction After a MOV SS,r/m or POP SS is a Store An Uncorrectable Error Logged in IA32_CR_MC2_STATUS May Also Result in a System Hang IA32_PERF_GLOBAL_CTRL MSR May Be Incorrectly Initialized Performance Monitor Counter INST_RETIRED.STORES May Count Higher than Expected Sleeping Cores May Not be Woken Up on Logical Cluster Mode Broadcast IPI Using Destination Field Instead of Shorthand Faulting Executions of FXRSTOR May Update State Inconsistently Performance Monitor Event EPT.EPDPE_MISS May be Counted While EPT is Disable Memory Aliasing of Code Pages May Cause Unpredictable System Behavior Performance Monitor Counters May Count Incorrectly Performance Monitor Event Offcore_response_0 (B7H) Does Not Count NT Stores to Local DRAM Correctly EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change Back to Back Uncorrected Machine Check Errors May Overwrite IA32_MC3_STATUS.MSCOD 10 Specification Update