Intel I3-530 Specifications - Page 11

Errata Sheet 3 of 5, A Fault May Not be Generated When the PS bit is set to 1 in a PML4E or - generation

|

View all Intel I3-530 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 11 highlights

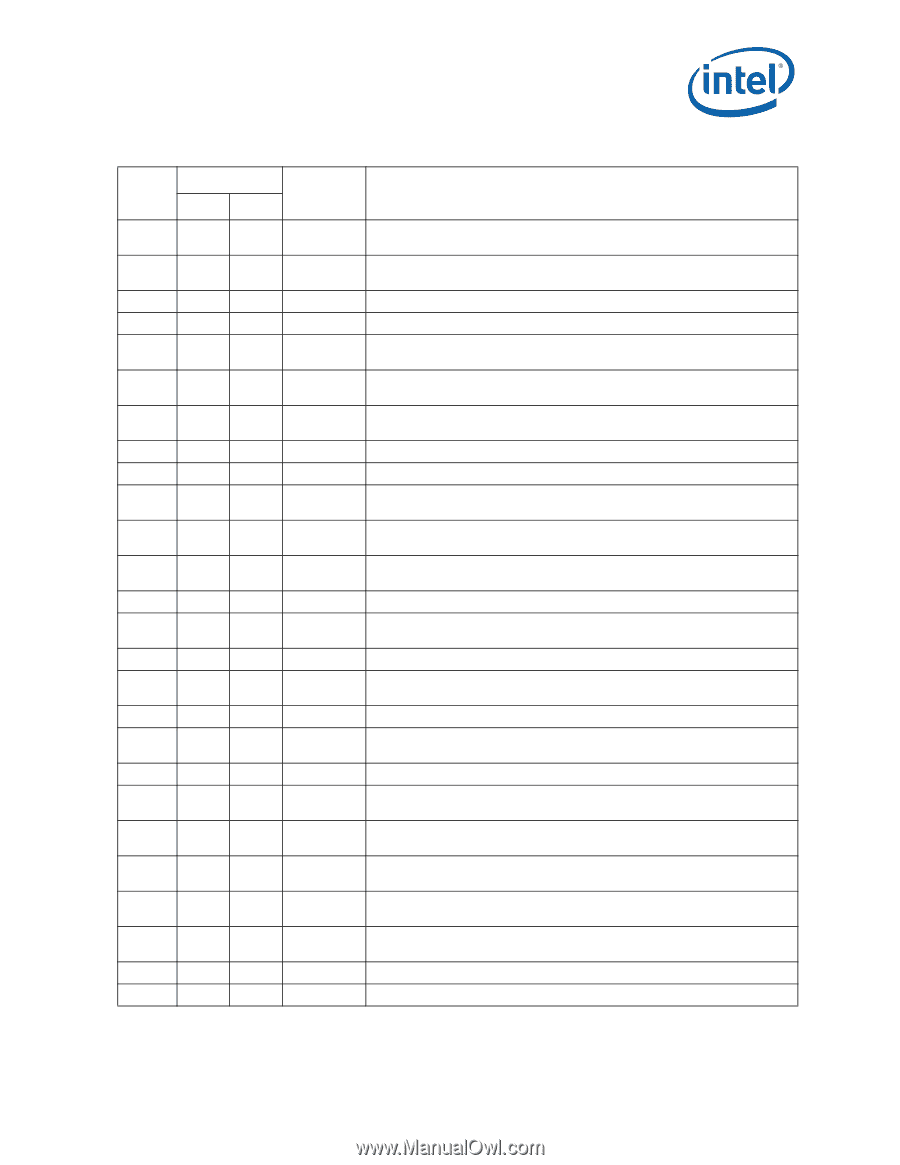

Errata (Sheet 3 of 5) Number Steppings C-2 K-0 Status AAU51 X X No Fix AAU52 X X No Fix AAU53 X X No Fix AAU54 X X No Fix AAU55 X X No Fix AAU56 X X No Fix AAU57 X X No Fix AAU58 X X No Fix AAU59 X X No Fix AAU60 X X No Fix AAU61 X X No Fix AAU62 X X No Fix AAU63 X X No Fix AAU64 X X No Fix AAU65 X X No Fix AAU66 X X No Fix AAU67 X X No Fix AAU68 X X No Fix AAU69 X X No Fix AAU70 X X No Fix AAU71 X X No Fix AAU72 X X No Fix AAU73 X X No Fix AAU74 X X No Fix AAU75 X Fixed AAU76 X X No Fix ERRATA Corrected Errors With a Yellow Error Indication May be Overwritten by Other Corrected Errors Performance Monitor Events DCACHE_CACHE_LD and DCACHE_CACHE_ST May Overcount Rapid Core C3/C6 Transitions May Cause Unpredictable System Behavior APIC Timer CCR May Report 0 in Periodic Mode Performance Monitor Events INSTR_RETIRED and MEM_INST_RETIRED May Count Inaccurately A Page Fault May Not be Generated When the PS bit is set to "1" in a PML4E or PDPTE BIST Results May be Additionally Reported After a GETSEC[WAKEUP] or INITSIPI Sequence Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected VM Exits Due to "NMI-Window Exiting" May Be Delayed by One Instruction The Memory Controller tTHROT_OPREF Timings May be Violated During Self Refresh Entry VM Exits Due to EPT Violations Do Not Record Information About Pre-IRET NMI Blocking Multiple Performance Monitor Interrupts are Possible on Overflow of IA32_FIXED_CTR2 LBRs May Not be Initialized During Power-On Reset of the Processor LBR, BTM or BTS Records May have Incorrect Branch From Information After an EIST Transition, T-states, C1E, or Adaptive Thermal Throttling VMX-Preemption Timer Does Not Count Down at the Rate Specified Multiple Performance Monitor Interrupts are Possible on Overflow of Fixed Counter 0 VM Exits Due to LIDT/LGDT/SIDT/SGDT Do Not Report Correct Operand Size Performance Monitoring Events STORE_BLOCKS.NOT_STA and STORE_BLOCKS.STA May Not Count Events Correctly Storage of PEBS Record Delayed Following Execution of MOV SS or STI Performance Monitoring Event FP_MMX_TRANS_TO_MMX May Not Count Some Transitions INVLPG Following INVEPT or INVVPID May Fail to Flush All Translations for a Large Page Logical Processor May Use Incorrect VPID after VM Entry That Returns From SMM The Memory Controller May Hang Due to Uncorrectable ECC Errors or Parity Errors Occurring on Both Channels in Mirror Channel Mode MSR_TURBO_RATIO_LIMIT MSR May Return Intel® Turbo Boost Technology Core Ratio Multipliers for Non-Existent Core Configurations Internal Parity Error May Be Incorrectly Signaled during C6 Exit PMIs during Core C6 Transitions May Cause the System to Hang 11 Specification Update