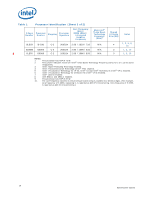

Intel I3-530 Specifications - Page 21

MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance

|

View all Intel I3-530 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 21 highlights

AAU12. General Protection Fault (#GP) for Instructions Greater than 15 Bytes May be Preempted Problem: When the processor encounters an instruction that is greater than 15 bytes in length, a #GP is signaled when the instruction is decoded. Under some circumstances, the #GP fault may be preempted by another lower priority fault (e.g., Page Fault (#PF)). However, if the preempting lower priority faults are resolved by the operating system and the instruction retried, a #GP fault will occur. Implication: Software may observe a lower-priority fault occurring before or in lieu of a #GP fault. Instructions of greater than 15 bytes in length can only occur if redundant prefixes are placed before the instruction. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. AAU13. General Protection (#GP) Fault May Not Be Signaled on Data Segment Limit Violation above 4-G Limit Problem: In 32-bit mode, memory accesses to flat data segments (base = 00000000h) that occur above the 4-G limit (0ffffffffh) may not signal a #GP fault. Implication: When such memory accesses occur in 32-bit mode, the system may not issue a #GP fault. Workaround: Software should ensure that memory accesses in 32-bit mode do not occur above the 4-G limit (0ffffffffh). Status: For the steppings affected, see the Summary Tables of Changes. AAU14. LBR, BTS, BTM May Report a Wrong Address when an Exception/ Interrupt Occurs in 64-bit Mode Problem: An exception/interrupt event should be transparent to the LBR (Last Branch Record), BTS (Branch Trace Store) and BTM (Branch Trace Message) mechanisms. However, during a specific boundary condition where the exception/interrupt occurs right after the execution of an instruction at the lower canonical boundary (0x00007FFFFFFFFFFF) in 64-bit mode, the LBR return registers will save a wrong return address with Bits 63 to 48 incorrectly sign extended to all 1's. Subsequent BTS and BTM operations which report the LBR will also be incorrect. Implication: LBR, BTS and BTM may report incorrect information in the event of an exception/ interrupt. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. AAU15. MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error Problem: A single Data Translation Look Aside Buffer (DTLB) error can incorrectly set the Overflow (bit [62]) in the MCi_Status register. A DTLB error is indicated by MCA error code (bits [15:0]) appearing as binary value, 000x 0000 0001 0100, in the MCi_Status register. Implication: Due to this erratum, the Overflow bit in the MCi_Status register may not be an accurate indication of multiple occurrences of DTLB errors. There is no other impact to normal processor functionality. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 21 Specification Update