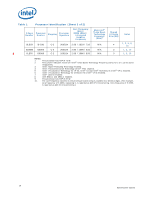

Intel I3-530 Specifications - Page 19

Values for LBR/BTS/BTM Will Be Incorrect after an Exit from SMM - cpu

|

View all Intel I3-530 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 19 highlights

Status: accessing side-effect memory and by ensuring that all code is written such that a code segment limit violation cannot occur as a part of reading from side-effect memory. For the steppings affected, see the Summary Tables of Changes. AAU6. MOV To/From Debug Registers Causes Debug Exception Problem: When in V86 mode, if a MOV instruction is executed to/from a debug registers, a general-protection exception (#GP) should be generated. However, in the case when the general detect enable flag (GD) bit is set, the observed behavior is that a debug exception (#DB) is generated instead. Implication: With debug-register protection enabled (i.e., the GD bit set), when attempting to execute a MOV on debug registers in V86 mode, a debug exception will be generated instead of the expected general-protection fault. Workaround: In general, operating systems do not set the GD bit when they are in V86 mode. The GD bit is generally set and used by debuggers. The debug exception handler should check that the exception did not occur in V86 mode before continuing. If the exception did occur in V86 mode, the exception may be directed to the general-protection exception handler. Status: For the steppings affected, see the Summary Tables of Changes. AAU7. Incorrect Address Computed for Last Byte of FXSAVE/FXRSTOR Image Leads to Partial Memory Update Problem: A partial memory state save of the 512-byte FXSAVE image or a partial memory state restore of the FXRSTOR image may occur if a memory address exceeds the 64KB limit while the processor is operating in 16-bit mode or if a memory address exceeds the 4GB limit while the processor is operating in 32-bit mode. Implication: FXSAVE/FXRSTOR will incur a #GP fault due to the memory limit violation as expected but the memory state may be only partially saved or restored. Workaround: Software should avoid memory accesses that wrap around the respective 16-bit and 32-bit mode memory limits. Status: For the steppings affected, see the Summary Tables of Changes. AAU8. Values for LBR/BTS/BTM Will Be Incorrect after an Exit from SMM Problem: After a return from SMM (System Management Mode), the CPU will incorrectly update the LBR (Last Branch Record) and the BTS (Branch Trace Store), hence rendering their data invalid. The corresponding data if sent out as a BTM on the system bus will also be incorrect. Problem: Note: This issue would only occur when one of the 3 above mentioned debug support facilities are used. Implication: The value of the LBR, BTS, and BTM immediately after an RSM operation should not be used. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. 19 Specification Update