Lenovo PC 300PL Technical Information Manual 6275, 6285 - Page 64

Appendix A. Connector Pin Assignments, AGP Monitor Port Connector, Memory Connectors

|

View all Lenovo PC 300PL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 64 highlights

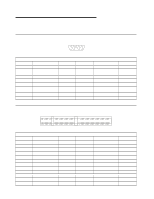

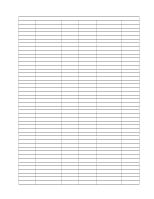

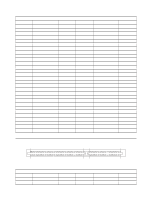

Appendix A. Connector Pin Assignments Appendix A. Connector Pin Assignments The following figures show the pin assignments for various system board connectors. AGP Monitor Port Connector 5 10 15 1 6 11 Figure 28. AGP Monitor Port Connector Pin Assignments Pin Signal I/O Pin 1 Red O 2 3 Blue O 4 5 Ground NA 6 7 Green ground NA 8 9 +5 V, used by DDC2B NA 10 11 Monitor ID 0 - Not I 12 used 13 Horizontal sync O 14 15 DDC2B clock I/O Signal I/O Green O Monitor ID 2 - Not I used Red ground NA Blue ground NA Ground NA DDC2B serial data I/O Vertical sync O Memory Connectors 85 168 1 84 Figure 29 (Page 1 of 3). System Memory Connector Pin Assignments Pin x64 Non-Parity x72 ECC Pin 1 VSS VSS 85 2 DQ0 DQ0 86 3 DQ1 DQ1 87 4 DQ2 DQ2 88 5 DQ3 DQ3 89 6 VCC VCC 90 7 DQ4 DQ4 91 8 DQ5 DQ5 92 9 DQ6 DQ6 93 10 DQ7 DQ7 94 11 DQ8 DQ8 95 12 VSS VSS 96 x64 Non-Parity VSS DQ32 DQ33 DQ34 DQ35 VCC DQ36 DQ37 DQ38 DQ39 DQ40 VSS x72 ECC VSS DQ32 DQ33 DQ34 DQ35 VCC DQ36 DQ37 DQ38 DQ39 DQ40 VSS 52 Copyright IBM Corp. June 1998