LG M6100 Service Manual - Page 43

Cpu Interface, Interface Register, Intermediate Register, Ymu787 Circuit Diagram

|

View all LG M6100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 43 highlights

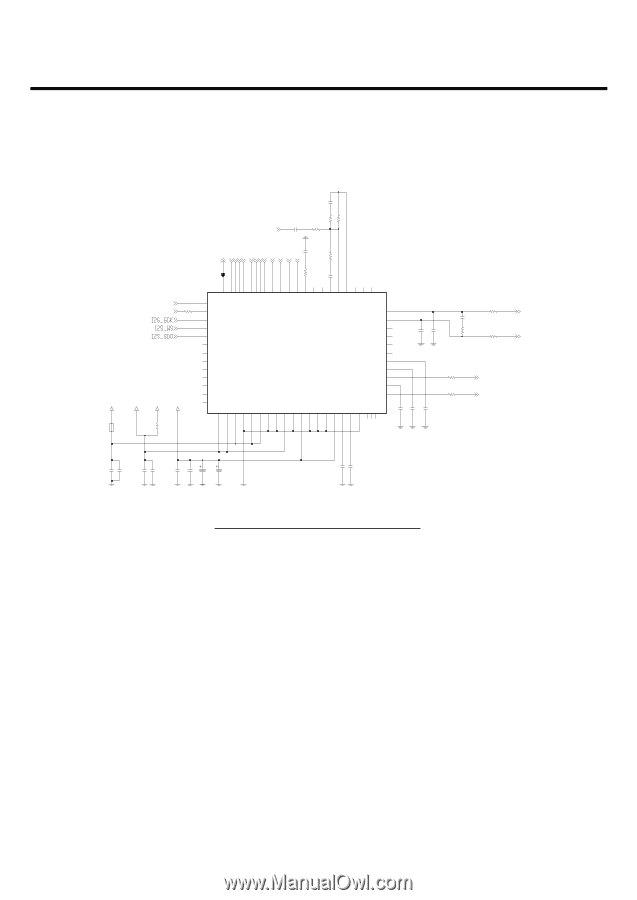

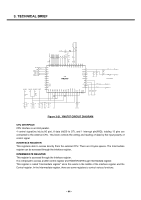

3. TECHNICAL BRIEF C733 120p R724 68K TP702 1V8_MV _MIDI_RST C738 0 13MHz 2V8_MV 2V8_VEXT VBAT B4 _RST G5 CLKI D2 BLCK D3 LRCK D1 SDI D6 GPIO0 C5 GPIO1 C1 GPIO2 C4 GPIO3 B1 LED2_GPIO5 C2 LDE1_GPIO4 C3 LED0 B2 MTR FB705 R734 NA C753 0.1u C759 C754 1u 0.1u C760 C761 C762 1u 1u 0.1u C755 4.7u C756 4.7u H1 IOVDD1 B3 IOVDD2 J4 DVDD1 J3 DVSS1 A2 DVDD2 F1 DVDD3 A3 DVSS2 E1 DVSS3 G8 AVDD F8 AVSS A6 SPVDDL A7 SPVSSL H7 SPVSSR1 J7 SPVSSR2 J6 SPVDDR F7 VREF F6 HPC D8 HPVSS A1 NC1 A8 NC2 J1 NC3 D4 _IRQ H2 D0 G3 D1 G2 D2 F3 D3 G1 D4 F2 D5 E3 D6 E2 D7 H4 _RD J2 _WR G4 A0 _CS H3 H5 PLLC C6 RXIN B6 EXTIN EQ1L B5 EQ2L A4 EQ3L A5 J5 EQ1R G6 EQ2R EQ3R H6 _MIDI_IRQ DATA08 DATA09 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 _RD _WR ADD00 _MIDI_CS R728 33K SPKPM C734 0.022u R726 33K C735 1000p R730 3.3K R725 68K C737 0.022u U708 YMU787 B8 SPOUT2L B7 SPOUT1L H8 SPOUT2R J8 SPOUT1R E8 TXOUT D7 EXTOUT EXC G7 BBL E6 C8 HPOUTL BBR E7 HPOUTR C7 C743 C744 47p 47p C748 0 C749 0 C750 C751 C752 0.1u 0.1u 1u C742 NA R732 NA R731 0 R733 0 Close to SPEAKER SPK_N SPK_P MIDI_HP_L MIDI_HP_R C757 C758 0.1u 1u Figure 3-21. YMU787 CIRCUIT DIAGRAM CPU INTERFACE CPU interface is an 8-bit parallel. 4 control signal(/wr,/rd,/cs,A0 pin), 8 data bit(D0 to D7), and 1 interrupt pin(/IRQ), totaling 13 pins are connected to the external CPU. This block controls the writing and reading of data by the input polarity of control signal INTERFACE REGISTER This registeris able to access directly ffrom the external CPU. There are 2 bytes spaces. The Intermediate register can be accessed through the interface register. INTERMEDIATE REGISTER This register is accessed through the Interface register. It is composed to access a latter control register and ROM/SRAM through Intermediate register. This register is called "Intermediate register" since this exists in the middle of the interface register and the Control register. In the Intermediate register, there are some registers to control various functions. - 44 -