LG M6100 Service Manual - Page 49

Memoryintel,u202

|

View all LG M6100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 49 highlights

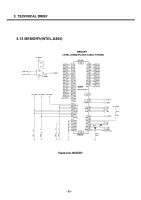

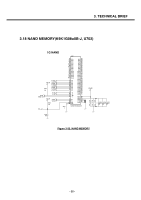

3. TECHNICAL BRIEF 3.13 MEMORY(INTEL,U202) 2V8_VMEM MEMORY (INTEL,256MbitFLASH+64Mbit PSRAM) A1 A2 A7 A8 NC1 NC2 NC3 NC4 4.7u 1u _ROM_CS2 _ROM_CS1 C219 0.1u 5 1 VCC 4 3 GND U202 2 TC7SH08FS _ROMCS1 2V8_VMEM 2V8_VMEM 1V8_VCORE ADD01 ADD02 ADD03 ADD04 ADD05 ADD06 ADD07 ADD08 ADD09 ADD10 ADD11 ADD12 ADD13 ADD14 ADD15 ADD16 ADD17 ADD18 ADD19 ADD20 ADD21 ADD22 ADD23 _ROM_CS1 1u 1u M8 M7 M2 M1 NC9 NC8 NC7 NC6 G1 H2 F1 A0 A1 D0 D1 H3 E1 D1 A2 D2 G3 H4 B1 A3 A4 D3 D4 J5 C1 F2 A5 D5 G5 J6 E2 A6 A7 D6 D7 H7 F6 D7 A8 D8 G2 J3 E7 A9 A10 D9 D10 G4 B8 C8 A11 D11 J4 H5 D8 A12 A13 D12 D13 G6 U205 F7 E8 A14 F8 A15 A16 D14 H6 J7 D15 D2 B2 A17 RD38F4050L0ZBQ0 B3 A18 A19 E6 B7 A20 _S_CS1 J1 C5 C7 A21 A22 S_CS2 C3 D3 A23 D6 E3 A24 A25 B5 L4 B6 K6 J8 K7 VCC11 VCC12 VCC21 VCC22 VCCQ1 VCCQ2 _P1_CS _P2_CS K2 P_MODE K8 _R_LB _R_WE C2 D5 H1 _R_OE _R_UB F3 L3 D4 VCCQ3 K5 VPP P_VCC _CE1 K1 K4 S_VCC _CE2 G8 K3 B4 VSS1 _CE3 _WP E4 C4 L1 VSS2 _ADV E5 F5 L2 VSS3 VSS4 _WE _OE1 J2 L5 L6 VSS5 _OE2 H8 F4 L7 VSS6 VSS7 _RST WAIT G7 L8 VSS8 CLK C6 DATA00 DATA01 DATA02 DATA03 DATA04 DATA05 DATA06 DATA07 DATA08 DATA09 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 R219 0 C226 220p _RAM_CS1 _RESET _LBS _WR _RD _UBS 2V8_VMEM R218 _ROMCS1 100K _ADV _WR _RD _RESET _WAIT BURSTCLK C225 C224 C223 C222 Figure 3-26. MEMORY - 50 -