Oki C7200 Service Manual - Page 23

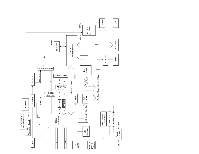

panel I/F, IDE I/F, Centronics I/F, USB I/F, PCI I/F, EEPROM and a SPD SDRAM DIMM

|

View all Oki C7200 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 23 highlights

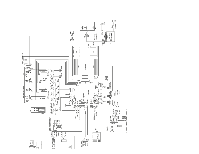

(1) CPU The CPU is PowerPC750, a 64-bit bus RISC processor, which inputs an 80-MHz CLK (=BUS CLK), and operates at 400MHz that is five times the input. (2) Secondary Cache SRAM SRAM is included as secondary cache of the CPU on the board. (3) ROM ROM is to be inserted into the three 168 pin DIMM slots. The slot A is for program ROM and the slot B is for Japanese kanji fonts. The slot C is not assigned. (4) RAM RAM is to be inserted into the four 168 pin DIMM slots. The DIMMs must be fitted in descending labeled type No. order into the slots 1, 3, 2 and 4. SDRAM DIMM Specifications: Speed: PC100 or more Capacity: 64/128/256 MB Configuration: Without parity. Without ECC. SPD information is required. Number of chips contained = 8 or 16. (5) EEPROM EEPROM, an 8-pin DIP package, is to be inserted into the IC socket. The EEPROM is of 16 Kbits for 3.3V power supply, and settings for controlling the controller block are stored in it. (6) Flash ROM A 2-Mbyte flash ROM is surface-mounted on the CRM board. The flash ROM is composed of four 256-k-by-16bit chips, and fonts and macros can be stored in it. (7) Memory control LSI (CI) A 696-pin BGA package ASIC made by NEC, which is equipped with a cooling heat sink and mainly controls a CPU I/F, memory, video data compression and decompression, and a PU-video I/F. (8) Interface control LSI (C2) A BGA package ASIC made by Toshiba, which controls a PU command I/F, operator panel I/F, IDE I/F, Centronics I/F, USB I/F, PCI I/F, EEPROM and a SPD (SDRAM DIMM) I/F. (9) IDE HDD An IDE connector is surface-mounted on the board to which an IDE HDD assembled using