Sharp ER-A450T Service Manual - Page 19

Block diagram, Pin description

|

View all Sharp ER-A450T manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 19 highlights

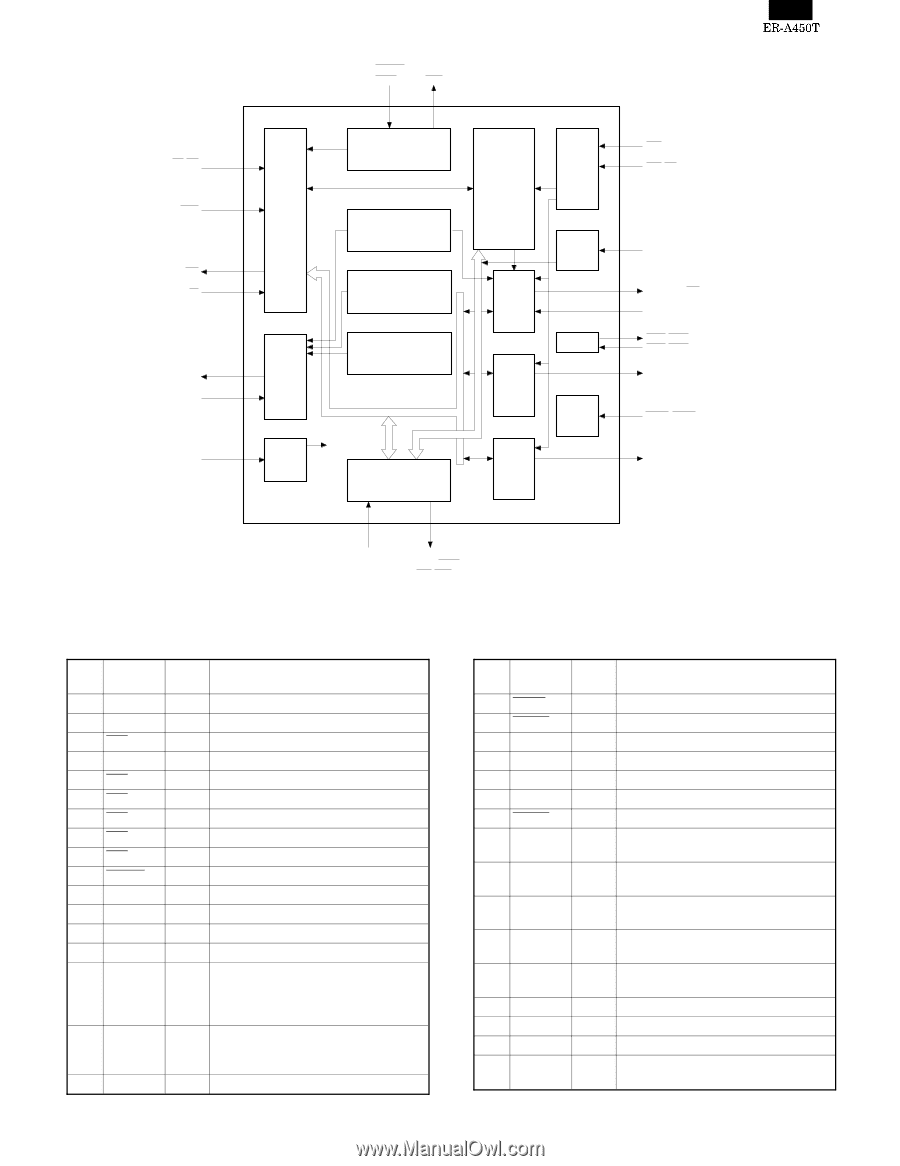

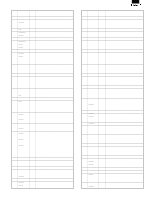

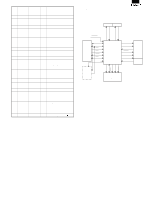

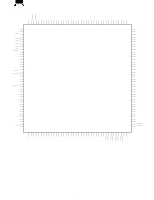

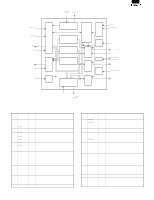

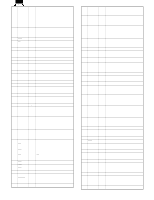

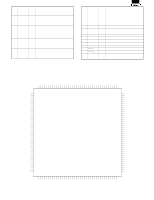

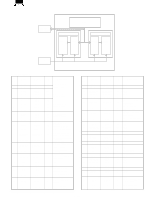

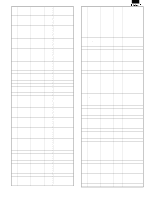

3) Block diagram RD, WR A0~23 D0~7 WO WI INT INTI PHAI (Φ) INTERRUPT CIRCUIT HOST BUS I/F UNIT CLOCK GEN. INHBEC CSEN CGS DECODEK UNIT HEAD CONTROL TIMER UNIT MOTOR CONTROL TIMER UNIT CUTTER CONTROL TIMER UNIT PB I/F UNIT PDCTLU SYSTEM I/F PORT HEAD I/F MISC. MOTOR CONTROL TEST CIRCUIT CUTTER CONTROL RES POF,INH POP,PHUP,PFP,PCRES PTRM,PTJM CLOCK,SO,ST1~5,HCO SI EBAK,EPEQ EBRK,EACK RVPON,JVPON, RAS,RBS,RCS,RDS, JAS,JBD,JCS,JDS TEST1,TEST2 CTAO,CTBO BD0~7 BA0~15 BRAS,BRAS BRD,BWR TPRC1 BLOCK DIAGRAM Fig. 2-8 4) Pin description Pin Signal No. name 1 GND 2 GND 3 ST1 4 GND 5 ST2 6 ST3 7 ST4 8 ST5 9 ST6 10 LATCH 11 GND 12 GND 13 GND 14 SI 15 SO 16 CLOCK 17 INHDEC In/Out Function - GND - GND O Head drive strobe signal 1 - GND O Head drive strobe signal 2 O Head drive strobe signal 3 O Head drive strobe signal 4 O NU O NU O Head latch signal - GND - GND - GND I Data return line, thermalhead -- TPRC1 O Send data from TPRC1 to thermalhead Data from PB-RAM or zero data are outputted at the falling of CLOCK signal. 16 O Thermalhead CLOCK signal SO is outputted at the edge of I Ä O, and is taken at the edge of o Ä I. I GND Pin Signal No. name 18 CSEN 19 TEST2 20 Vcc 21 Vcc 22 Vcc 23 Vcc 24 TEST1 25 D0 26 D1 27 D2 28 D3 29 D4 30 GND 31 GND 32 GND 33 D5 In/Out Function I GND I +5V internal counter timer test pin - +5V - +5V - +5V - +5V I +5V internal counter timer test pin I/O Data bus 0: Internal register, print buffer data IO I/O Data bus 1: Internal register, print buffer data IO I/O Data bus 2: Internal register, print buffer data IO I/O DAta bus 3: Internal register, print buffer data IO I/O Data bus 4: Internal register, print buffer data IO - GND - GND - GND I/O Data bus 5: Internal register, print buffer data IO 4 - 11