Sharp ER-A450T Service Manual - Page 23

Sharp ER-A450T Manual

|

View all Sharp ER-A450T manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 23 highlights

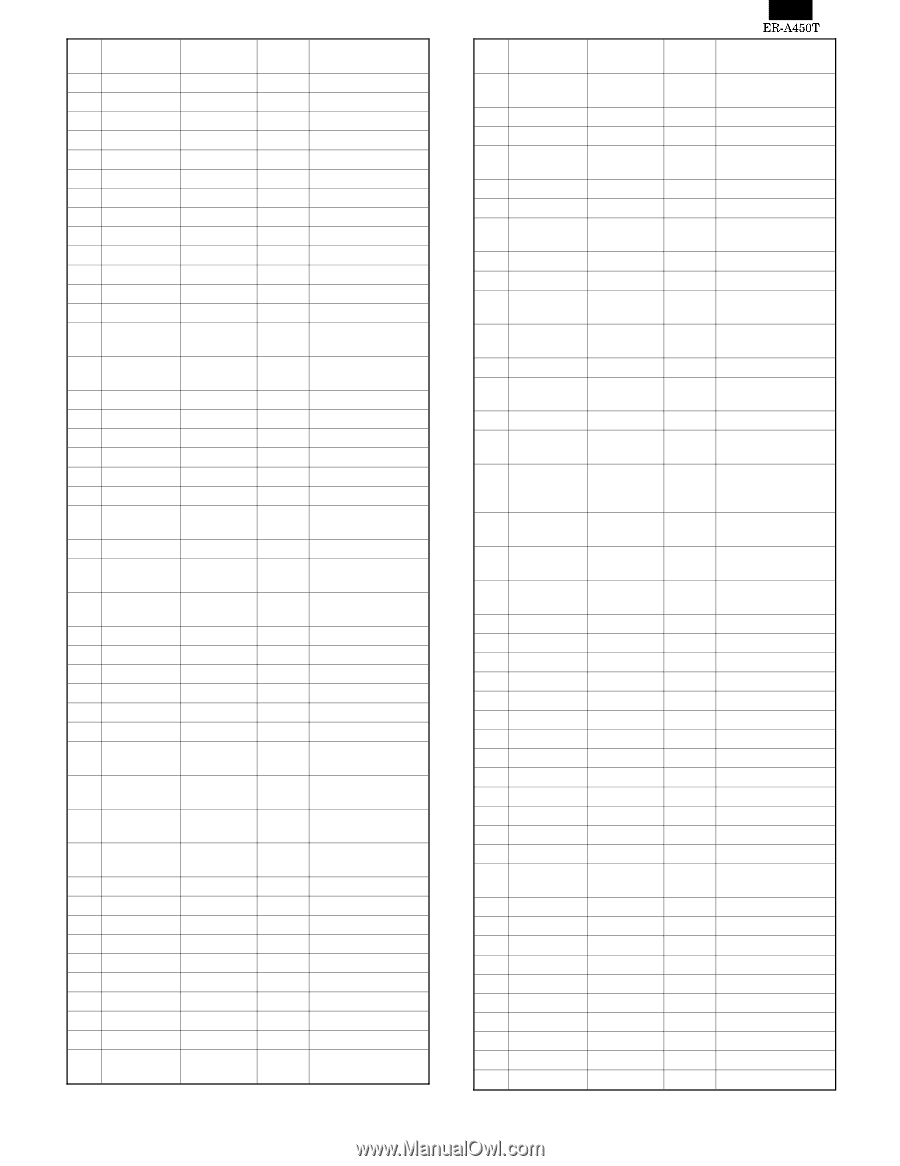

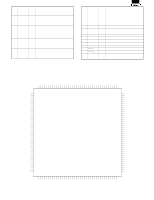

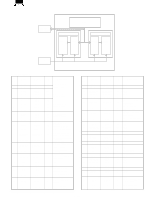

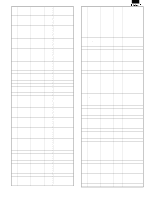

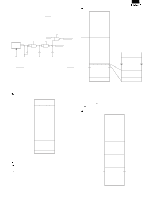

Pin NO. Name ER-A770 I/O Description 54 D2 D2 IO Data bus (CPU) 55 D3 D3 IO Data bus (CPU) 56 GND GND GND 57 D4 D4 IO Data bus (CPU) 58 D5 D5 IO Data bus (CPU) 59 D6 D6 IO Data bus (CPU) 60 D7 D7 IO Data bus (CPU) 61 GND GND GND 62 VCC VCC +5V 63 X1 NC O OSI14 NC 64 X2 # I OSI14 System clock 65 XOUT CLK_USART O Clock (USART) 66 TRCK NC O NC 67 AB0 AH0 O Address bus for USART 68 AB1 AH1 O Address bus for USART 69 US1CH GND IS GND 70 PX NC O NC 71 /POF /POFF IS POFF signal 72 /RSRQ /IRQ1 3S RS232 INTRRUPT 73 /TRV GND IS GND 74 RXDATA0 NC O NC 75 TXE /SRESET O INLINE SOFT RESET 76 /TRRQ /TRQ2 3S INLINE INTRRUPT 77 /TRQ1 /TRQ1 ON6 TIMER INTRRUPT (RS232) 78 /TRQ2 NC ON6 TIMER INTRRUPT (INLINE) 79 A0 A0 I Address bus for CPU 80 A1 A1 I Address bus for CPU 81 A2 A2 I Address bus for CPU 82 A3 A3 I Address bus for CPU 83 A4 A4 I Address bus for CPU 84 A5 A5 I Address bus for CPU 85 /OPTCS /OPTCS I Option chip select (from MPCA) 86 /RD /RDO I Read signal (from CPU) 87 /WR /WRO I Write signal (from CPU) 88 /RES /RES IS Reset signal (from CPU) 89 DB0 DB0 IO DATA BUS (USART) 90 DB1 DB1 IO DATA BUS (USART) 91 DB2 DB2 IO DATA BUS (USART) 92 DB3 DB3 IO DATA BUS (USART) 93 GND GND GND 94 DB4 DB4 IO DATA BUS (USART) 95 DB5 DB5 IO DATA BUS (USART) 96 DB6 DB6 IO DATA BUS (USART) 97 DB7 DB7 IO DATA BUS (USART) 98 /R /RDH O Read signal (to USART) Pin NO. Name ER-A770 I/O Description 99 /W /WRH O Write signal (to USART) 100 VCC VCC +5V 101 GND GND GND 102 RES RES USART O Reset signal (to USART) 103 TRNCLK GND I GND 104 RCVCLK GND I GND 105 DBTST /SRCS ID RS-232/INLINE USART chip select 106 UTST VCC ID +5V 107 /CSA /CS1 IS USART_A chip select 108 TRNDTA TXD1 O RS-232 transmission data signal 109 /DTRA /DTR1 O RS-232 data terminal ready signal 110 /RTSA NC O NC 111 RCVDTA RCVDT1 IS RS-232 reception data signal 112 /CTSA GND IS GND 113 /DSRA /DSR1 IS RS-232 data set ready signal 114 TRNRDYA TRNRDY1 RS-232 data O transmission enable signal 115 RCVRDYA RCVRDY1 O RS-232 data reception enable signal 116 TRNEMPA TRNEMP1 O RS-232 transmission buffer empty signal 117 SYCBKA BRK1 IO Break code detection signal 118 GND GND GND 119 /CSB /CS2 IS USART_B chip select 120 TRNDTB TXD2 O NC 121 /DTRB /DTR2 O NC 122 /RTSB NC O NC 123 RCVDTB RCVDT2 IS GND 124 /CTSB GND IS GND 125 /DSRB /DSR2 IS GND 126 TRNRDYB TRNRDY2 O NC 127 RCVRDYB RCVRDY2 O NC 128 TRNEMPB TRNEMP2 O NC 129 SYCBKB BRK2 IO NC 130 GND GND GND 131 /CSC /CS3 IS USART_C chip select 132 TRNDTC TXD3 O NC 133 /DTRC /DTR3 O NC 134 /RTSC /RTS3 O NC 135 RCVDTC RCVDT3 IS GND 136 /CTSC GND IS GND 137 /DSRC /DSR3 IS GND 138 TRNRDYC TRNRDY3 O NC 139 RCVRDYC RCVRDY3 O NC 140 TRNEMPC TRNEMP3 O NC 141 SYCBKC NC IO NC 4 - 15