TEAC DW-224E-V Hardware Specification - Page 19

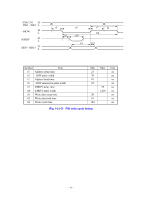

Fig. 14.4-4, PIO read cycle timing

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 19 highlights

-CS0, CS1 H DA0 ~ DA2 L -DIOR H L IORDY H L DD0 ~ DD15 H L t15 t16 t19 t20 t17 t18 t24 t22 Symbol Item t15 Address setup time t16 -DIOR pulse width t17 Address hold time t18 -DIOR interactive pulse width t19 IORDY delay time t20 IORDY pulse width t22 Read data hold time t24 Read cycle time Min Max Unit 25 ns 70 ns 10 ns 25 ns 35 ns 90 1,250 ns 5 ns 120 ns (Fig. 14.4-4) PIO read cycle timing - 17 -

° 17 °

(Fig. 14.4-4)

PIO read cycle timing

Symbol

Item

Min

Max

Unit

t15

Address setup time

25

ns

t16

°DIOR pulse width

70

ns

t17

Address hold time

10

ns

t18

°DIOR interactive pulse width

25

ns

t19

IORDY delay time

35

ns

t20

IORDY pulse width

90

1,250

ns

t22

Read data hold time

5

ns

t24

Read cycle time

120

ns

H

L

H

L

H

L

H

L

°CS0, CS1

DA0 ~ DA2

°DIOR

IORDY

DD0 ~ DD15

t15

t16

t17

t18

t19

t20

t22

t24