TEAC DW-224E-V Hardware Specification - Page 21

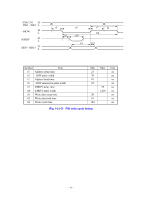

Fig. 14.4-6, DMA multi word transfer timing

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 21 highlights

DMARQ H L -DMACK H L -DIOW H L DD0 ~ DD15 H L -DIOR H L DD0 ~ DD15 H L t45 t38 t39 t48 t40 t46 t41 t42 t43 t44 t49 Symbol Item Min Max Unit t38 From -DMACK assert to -DIOW low 0 ns t39 -DIOW, -DIOR pulse width 70 ns t40 -DIOW, -DIOR interactive pulse width 25 ns t41 Write data setup time 20 ns t42 Write data hold time 10 ns t43 Read data delay time 50 ns t44 Read data hold time 5 ns t45 From -DIOW, -DIOR low to DMARQ negate 35 ns t46 From -DIOW, -DIOR high to -DMACK negate 5 ns t48 Write cycle time 120 ns t49 Read cycle time 120 ns (Fig. 14.4-6) DMA multi word transfer timing - 19 -

° 19 °

(Fig. 14.4-6)

DMA multi word transfer timing

Symbol

Item

Min

Max

Unit

t38

From °DMACK assert to °DIOW low

0

ns

t39

°DIOW, °DIOR pulse width

70

ns

t40

°DIOW, °DIOR interactive pulse width

25

ns

t41

Write data setup time

20

ns

t42

Write data hold time

10

ns

t43

Read data delay time

50

ns

t44

Read data hold time

5

ns

t45

From °DIOW, °DIOR low to DMARQ negate

35

ns

t46

From °DIOW, °DIOR high to °DMACK negate

5

ns

t48

Write cycle time

120

ns

t49

Read cycle time

120

ns

H

L

H

L

H

L

H

L

H

L

DMARQ

°DMACK

°DIOW

DD0 ~ DD15

°DIOR

H

L

DD0 ~ DD15

t45

t38

t39

t40

t48

t46

t41

t42

t43

t49

t44