TEAC DW-224E-V Hardware Specification - Page 24

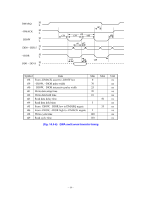

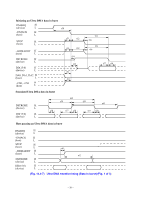

Fig.14.4-7 Ultra DMA transfer timing Data in burst Fig. 3 of 3

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

Symbol Item Min Max Unit t50 Unlimited interlock time 0 ns t51 Setup time/Hold time (to -DMACK ↓ ) 20 ns t52 Envelope time (-DMACK ↓ to STOP/ -HDMARDY ↓ ) 20 70 ns t53 DSTROSE negate start time (STOP/-HDMARDY 0 ↓ to DSTROBE ↓ ) 170 ns t54 DSTROBE drive delay time (to -DMACK ↓) 0 ns t55 Output data, release delay time (to -DMACK ↓) 10 ns t56 Output data, drive start time (to STOP ↓/ 0 ns -HDMARDY ↓) t57 Valid data, setup time (to DSTROBE edge) 30 ns t58 Valid data, hold time (to DSTROBE edge) 6 ns t59 DSTROBE cycle time Mode 2 54 ns Mode 1 73 ns Mode 0 112 ns t60 DSTROBE x 2-cycle time Mode 2 115 ns Mode 1 154 ns Mode 0 230 ns DSTROBE Average x 2-cycle time Mode 2 120 ns Mode 1 160 ns Mode 0 240 ns t61 DSTROBE stop shift time (DSTROBE Mode 2 edge to -HDMARDY ↑) Mode 1 20 ns 30 ns Mode 0 50 ns t62 Final DSTROBE stop time (to -HDMARDY ↑) 60 ns t63 DSTROBE ↑ to -DMACK ↑ delay time 20 ns t64 Limited interlock time 0 150 ns t65 DSTROBE release time (to -DMACK ↑) 20 ns t66 DSTROBE edge to HDMARQ ↓ delay time 50 ns t67 HDMARQ ↓ to CRC data output delay time 20 ns t68 Data setup time (to -DMACK ↑) 30 ns t69 Data hold time (to -DMACK ↑) 6 ns (Fig.14.4-7) Ultra DMA transfer timing (Data in burst) (Fig. 3 of 3) - 22 -