TEAC DW-224E-V Hardware Specification - Page 23

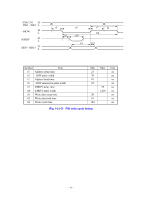

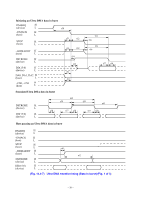

Fig.14.4-7 Ultra DMA transfer timing Data in burst Fig. 2 of 3

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 23 highlights

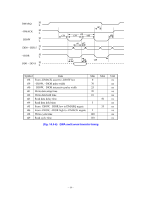

Device terminating an Ultra DMA data in burst DMARQ H (device) L -DMACK H (host) L t64 t64 STOP H (host) L t64 −HDMARDY H (host) L t66 DSTROBE H (device) L t67 t55 DD(15:0) H (device) L DA0, DA1, DA2 H (host) L −CS0, −CS1 H (host) L Host terminating an Ultra DMA data in burst t63 t51 t51 t65 t68 t69 CRC t51 t51 DMARQ H (device) L -DMACK H (host) L STOP H (host) L −HDMARDY H (host) L t62 DSTROBE H (device) L DD(15:0) H (device) L DA0, DA1, DA2 H (host) L −CS0, −CS1 H (host) L t64 t63 t67 t55 t64 t63 t51 t51 t65 t68 t69 CRC t51 t51 (Fig.14.4-7) Ultra DMA transfer timing (Data in burst) (Fig. 2 of 3) - 21 -

° 21 °

(Fig.14.4-7) Ultra DMA transfer timing (Data in burst) (Fig. 2 of 3)

t63

t64

t51

t65

t66

t67

t68

t69

t51

t51

t51

t55

t64

t63

t67

t51

t62

t68

t69

t51

t51

t51

t55

t64

t64

CRC

t64

CRC

t63

t65

Device terminating an Ultra DMA data in burst

H

L

H

L

H

L

H

L

H

L

DMARQ

(device)

°DMACK

(host)

STOP

(host)

−

HDMARDY

(host)

H

L

DSTROBE

(device)

DD(15:0)

(device)

DA0, DA1, DA2

(host)

H

L

−

CS0,

−

CS1

(host)

H

L

Host terminating an Ultra DMA data in burst

H

L

H

L

H

L

H

L

H

L

DMARQ

(device)

°DMACK

(host)

STOP

(host)

−

HDMARDY

(host)

H

L

DSTROBE

(device)

DD(15:0)

(device)

DA0, DA1, DA2

(host)

H

L

−

CS0,

−

CS1

(host)

H

L