TEAC DW-224E-V Hardware Specification - Page 22

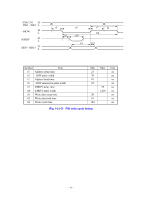

Fig. 14.4-7, Ultra DMA transfer timing Data in burst Fig. 1 of 3

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 22 highlights

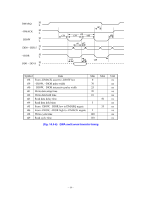

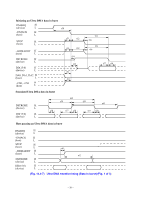

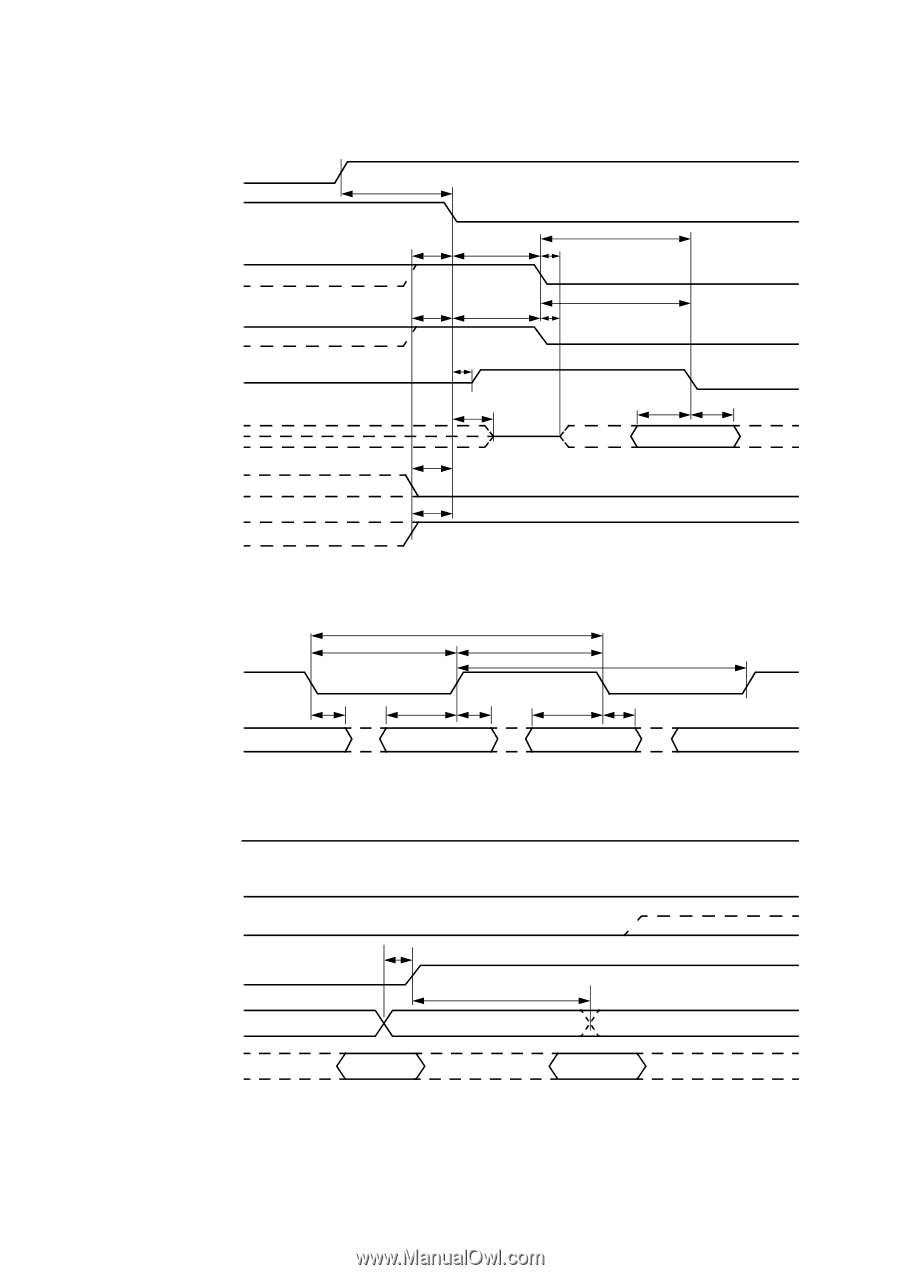

Initiating an Ultra DMA data in burst DMARQ H (device) L -DMACK H (host) L STOP H (host) L t50 t51 t52 −HDMARDY H (host) L DSTROBE H (device) L DD(15:0) H (device) L DA0, DA1, DA2 H (host) L −CS0, −CS1 H (host) L t51 t52 t54 t55 t51 t51 Sustained Ultra DMA data in burst t53 t56 t53 t56 t57 t58 DSTROBE H (device) L DD(15:0) H (device) L t60 t59 t58 t57 t58 Host pausing an Ultra DMA data in burst t59 t60 t57 t58 DMARQ H (device) L -DMACK H (host) L STOP H (host) L −HDMARDY H (host) L DSTROBE H (device) L DD(15:0) H (device) L t61 t62 (Fig. 14.4-7) Ultra DMA transfer timing (Data in burst) (Fig. 1 of 3) - 20 -

° 20 °

(Fig. 14.4-7)

Ultra DMA transfer timing (Data in burst) (Fig. 1 of 3)

t50

t51

t52

t53

t54

t55

t56

t57

t58

t52

t51

t51

t51

t53

t56

t60

t59

t58

t57

t60

t59

t58

t58

t57

t61

t62

H

L

H

L

H

L

H

L

H

L

DMARQ

(device)

°DMACK

(host)

STOP

(host)

−

HDMARDY

(host)

H

L

Initiating an Ultra DMA data in burst

DSTROBE

(device)

DD(15:0)

(device)

DA0, DA1, DA2

(host)

H

L

−

CS0,

−

CS1

(host)

H

L

Sustained Ultra DMA data in burst

H

L

H

L

DSTROBE

(device)

DD(15:0)

(device)

Host pausing an Ultra DMA data in burst

H

L

H

L

H

L

H

L

H

L

DMARQ

(device)

°DMACK

(host)

STOP

(host)

−

HDMARDY

(host)

H

L

DSTROBE

(device)

DD(15:0)

(device)