TEAC DW-224E-V Hardware Specification - Page 20

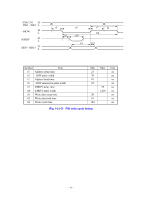

Fig. 14.4-5, DMA single word transfer timing

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 20 highlights

DMARQ H L -DMACK H L -DIOW H L DD0 ~ DD15 H L -DIOR H L DD0 ~ DD15 H L t26 t34 t36 t27 t28 t30 t31 t32 t33 Symbol Item Min Max Unit t26 From -DMACK assert to -DMAREQ negate 80 ns t27 From -DMACK assert to -DIOW low 0 ns t28 -DIOW, -DIOR pulse width 120 ns t30 Write data setup time 35 ns t31 Write data hold time 20 ns t32 Read data delay time 60 ns t33 Read data hold time 5 ns t34 From -DIOW, -DIOR high to -DMACK negate 0 ns t36 Cycle time 240 ns (Fig. 14.4-5) DMA single word transfer timing - 18 -

° 18 °

(Fig. 14.4-5)

DMA single word transfer timing

Symbol

Item

Min

Max

Unit

t26

From °DMACK assert to °DMAREQ negate

80

ns

t27

From °DMACK assert to °DIOW low

0

ns

t28

°DIOW, °DIOR pulse width

120

ns

t30

Write data setup time

35

ns

t31

Write data hold time

20

ns

t32

Read data delay time

60

ns

t33

Read data hold time

5

ns

t34

From °DIOW, °DIOR high to °DMACK negate

0

ns

t36

Cycle time

240

ns

H

L

H

L

H

L

H

L

H

L

DMARQ

°DMACK

°DIOW

DD0 ~ DD15

°DIOR

H

L

DD0 ~ DD15

t26

t34

t27

t28

t36

t30

t31

t32

t33