TEAC DW-224E-V Hardware Specification - Page 25

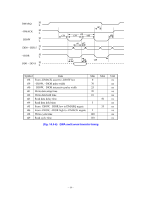

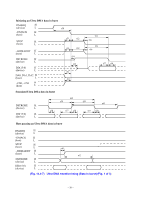

Fig. 14.4-8, Ultra DMA transfer timing Data out burst Fig. 1 of 3

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 25 highlights

Initiating an Ultra DMA data out burst DMARQ H (device) L -DMACK H (host) L STOP H (host) L −DDMARDY H (device) L HSTROBE H (host) L DD(15:0) H (host) L DA0, DA1, DA2 H (host) L −CS0, −CS1 H (host) L Sustained Ultra DMA data out burst t70 t71 t72 t73 t71 t71 t71 HSTROBE H (host) L DD(15:0) H (host) L t78 t77 t77 t76 t75 t76 Device pausing an Ultra DMA data out burst t74 t70 t75 t76 t78 t75 t76 DMARQ H (device) L -DMACK H (host) L STOP H (host) L −DDMARDY H (device) L HSTROBE H (host) L DD(15:0) H (host) L t80 t79 (Fig. 14.4-8) Ultra DMA transfer timing (Data out burst) (Fig. 1 of 3) - 23 -

° 23 °

(Fig. 14.4-8)

Ultra DMA transfer timing (Data out burst) (Fig. 1 of 3)

t70

t71

t72

t73

t74

t75

t76

t70

t71

t71

t71

t78

t77

t75

t76

t77

t78

t75

t76

t80

t79

t76

Initiating an Ultra DMA data out burst

H

L

H

L

H

L

H

L

H

L

DMARQ

(device)

°DMACK

(host)

STOP

(host)

−

DDMARDY

(device)

H

L

HSTROBE

(host)

DD(15:0)

(host)

DA0, DA1, DA2

(host)

H

L

−

CS0,

−

CS1

(host)

H

L

Sustained Ultra DMA data out burst

H

L

H

L

HSTROBE

(host)

DD(15:0)

(host)

Device pausing an Ultra DMA data out burst

H

L

H

L

H

L

H

L

H

L

DMARQ

(device)

°DMACK

(host)

STOP

(host)

−

DDMARDY

(device)

H

L

HSTROBE

(host)

DD(15:0)

(host)