HP Vectra XU 6/XXX HP Vectra XU 6/XXX - Guide to Optimization Performance - Page 40

Main Memory

|

View all HP Vectra XU 6/XXX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 40 highlights

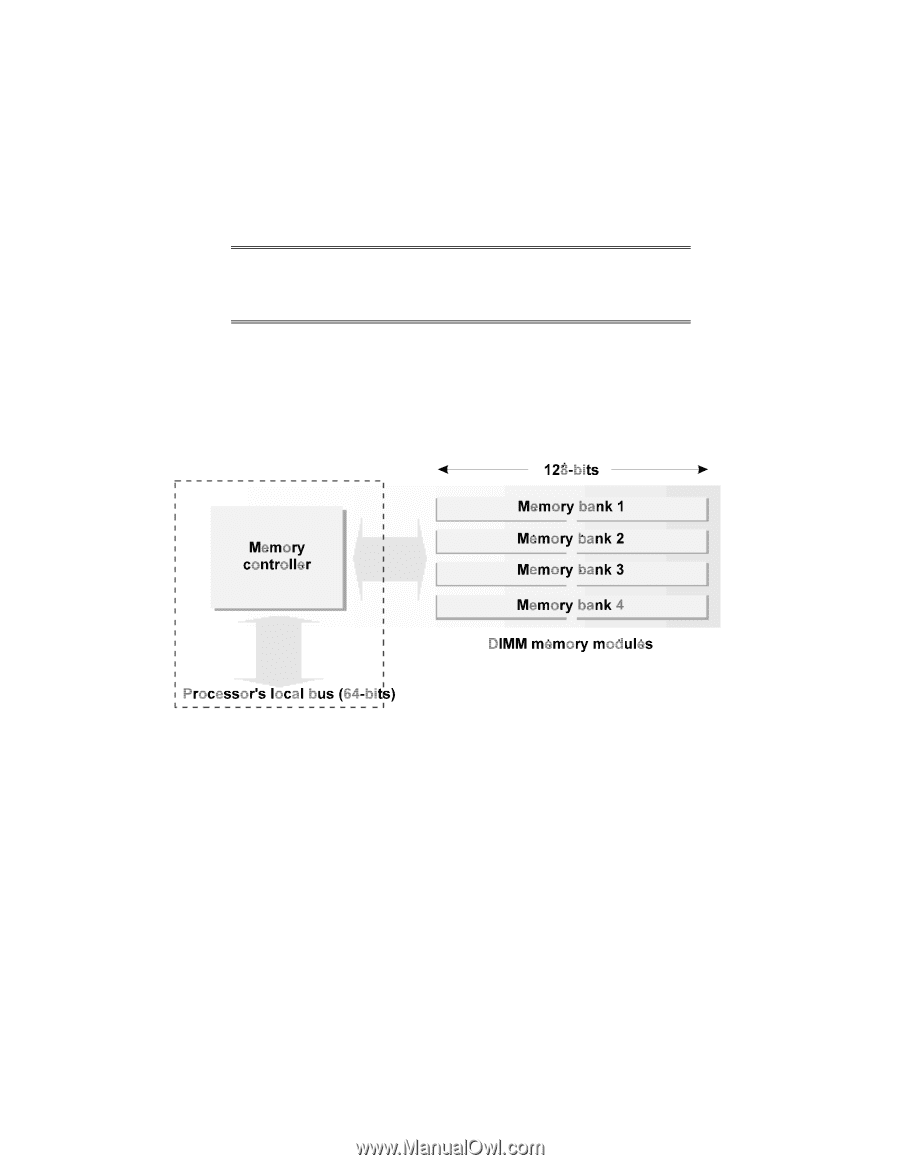

MAIN MEMORY The main memory in your PC consists of two, four, six or eight Double Interline Memory Modules (DIMMs). 16 MB of memory is fitted as standard (two 8 MB modules) and can be upgraded to a maximum of 256 MB. Memory modules are available in three capacities: 8 MB, 16 MB and 32 MB. The maximum memory capacity (256 MB) is obtained by installing eight 32 MB DIMM modules. NOTE The DIMM modules used by your HP Vectra XU PC use a 5 volt power source. DIMM modules that use a 3.3 volt power source are not supported and must not be installed. 128-bit Memory Each DIMM module stores 64 bits of data plus 8-bits of Error Correcting Code (ECC) code. Access to the memory modules is controlled by a memory controller on the processor's local bus. This controller manages the modules in pairs to create single, 128-bit wide logical banks. The processor's local data bus is 64 bits wide. All data written to or read from the memory is transferred on this bus. The memory modules are accessed by the memory controller through two, parallel 64-bit data paths. The memory controller connects these two 64-bit data paths with the processor's bus by interleaving the accesses. This means that consecutive 64-bit accesses to a memory bank are made to different modules. By using interleaving to access the memory banks, the memory controller actually increases the speed of your PC's memory. This is because of the characteristics of the memory components used. Main memory uses a type of memory component called Dynamic Random Access Memory (DRAM). DRAM stores data in a rectangular array, so that each data item corresponds to an address (location) which is formed of two parts. These two parts must be sent to the DRAM in separate clock cycles, which means that the data cannot be read from or written to the DRAM in the same clock cycle as the memory controller begins to access it.