| Section |

Page |

| technical reference |

1 |

| technical reference |

1 |

| technical reference |

1 |

| hp workstation x1000 |

1 |

| Manufacturing Part Number:� n.a. |

1 |

| Edition E1001 |

1 |

| © Copyright 2001 |

1 |

| © Copyright 2001 |

1 |

| Hewlett-Packard Company |

1 |

| Legal Notices |

2 |

| Legal Notices |

2 |

| Hewlett-Packard Co. |

3 |

| Hewlett-Packard Co. |

3 |

| Technical Computer Division |

3 |

| 3404 E. Harmony Rd. Fort Collins, CO 80525 |

3 |

| preface |

13 |

| preface |

13 |

| important warnings |

13 |

| important warnings |

13 |

| avoid electrical shocks |

13 |

| avoid electrical shocks |

13 |

| WARNING To avoid electrical shock, do not open the power supply. There are no user-serviceable pa... |

13 |

| electrical |

13 |

| electrical |

13 |

| WARNING For your safety always connect the equipment to a grounded wall outlet. Always use a powe... |

13 |

| multimedia models |

13 |

| multimedia models |

13 |

| WARNING If your PC is a multimedia model, or if you have installed a sound card in your PC, alway... |

13 |

| removing and replacing the cover |

14 |

| removing and replacing the cover |

14 |

| WARNING For your safety, never remove the PC cover without first disconnecting the power cord fro... |

14 |

| safety information |

14 |

| safety information |

14 |

| WARNING There is a danger of explosion if the battery is incorrectly installed. For your safety, ... |

14 |

| static electricity |

15 |

| static electricity |

15 |

| CAUTION Static electricity can damage electronic components. Turn OFF all equipment. Don’t let yo... |

15 |

| workstation documentation roadmap |

15 |

| workstation documentation roadmap |

15 |

| <TABLE> |

15 |

| Table�1 |

15 |

| <TABLE HEADING> |

15 |

| <TABLE ROW> |

15 |

| If you want to... |

15 |

| Go to this source... |

15 |

| And refer to... |

15 |

| <TABLE BODY> |

15 |

| <TABLE ROW> |

15 |

| Find Information |

15 |

| Your computer |

15 |

| Start >Programs > HP Info > Finding Information |

15 |

| <TABLE ROW> |

15 |

| Set up your computer |

15 |

| Getting Started Guide |

15 |

| Chapter 1 “Setting Up and Using Your Workstation.” |

15 |

| <TABLE ROW> |

15 |

| Learn how to use your operating system |

15 |

| Your computer |

15 |

| Operating System Online Help |

15 |

| <TABLE ROW> |

15 |

| Learn how to upgrade your computer by installing accessories |

15 |

| This Technical Reference Manual |

15 |

| Chapter 6 “Removing and Replacing Hardware Parts” |

15 |

| <TABLE ROW> |

15 |

| Find out about the different support options available |

15 |

| www.hp.com/workst ations/support |

15 |

| The support options section |

15 |

| <TABLE ROW> |

15 |

| Find out how to troubleshoot your PC Workstation |

15 |

| This Technical Reference Manual |

15 |

| Chapter 7 “Troubleshooting Your Workstation” |

15 |

| technical information |

16 |

| technical information |

16 |

| <TABLE> |

16 |

| <TABLE BODY> |

16 |

| <TABLE ROW> |

16 |

| Characteristics |

16 |

| HP Workstation x1000 |

16 |

| <TABLE ROW> |

16 |

| Weight (configuration with one CD-ROM drive, excluding keyboard and display) |

16 |

| 14.3 kg (31.5 pounds) |

16 |

| <TABLE ROW> |

16 |

| Dimensions |

16 |

| Width: �20.6cm (8.1in.) Height: 47.5cm (18.7in.) Depth: 44.2cm (17.4in.) |

16 |

| <TABLE ROW> |

16 |

| Footprint |

16 |

| 0.09 m2 (0.98 sq ft). |

16 |

| <TABLE ROW> |

16 |

| Acoustic noise emission (ISO�7779) |

16 |

| Sound power level |

16 |

| <TABLE ROW> |

16 |

| Power Supply |

16 |

| 100 - 127 VAC, 7.0 A rms |

16 |

| <TABLE ROW> |

16 |

| Storage Humidity |

16 |

| 8% to 85% (relative) |

16 |

| <TABLE ROW> |

16 |

| Operating Temperature |

16 |

| +10 �C to +35 �C (+50 �F to +95�F). |

16 |

| 1 system overview |

17 |

| 1 system overview |

17 |

| • Introduces the system’s internal and external features |

17 |

| • Introduces the system’s internal and external features |

17 |

| • Lists the system’s specifications and characteristic data |

17 |

| • Provides a summary of the available documentation |

17 |

| workstation description |

18 |

| workstation description |

18 |

| <TABLE> |

18 |

| <TABLE HEADING> |

18 |

| <TABLE ROW> |

18 |

| Feature |

18 |

| Description |

18 |

| <TABLE BODY> |

18 |

| <TABLE ROW> |

18 |

| System Board |

18 |

| System Board |

18 |

| Dimensions: 9.5in. ¥ 9.5 in. in an Extended-ATX (E-ATX) package |

18 |

| <TABLE ROW> |

18 |

| Processor |

18 |

| Processor |

18 |

| Intel Pentium�4 processor |

18 |

| <TABLE ROW> |

18 |

| Cache Memory (integrated in processor package) |

18 |

| Cache Memory (integrated in processor package) |

18 |

| • Level 1: 12KB code, 8KB data |

18 |

| • Level 1: 12KB code, 8KB data |

18 |

| • Level 1: 12KB code, 8KB data |

18 |

| • Level 2: 256KB |

18 |

| <TABLE ROW> |

18 |

| Internal Processor Clock Speed |

18 |

| Internal Processor Clock Speed |

18 |

| 1.7GHz, 1.9GHz, and 2.0 GHz |

18 |

| <TABLE ROW> |

18 |

| Chipset |

18 |

| Chipset |

18 |

| Intel�i845 chipset, including Memory Controller Hub (MCH) Host Bridge, Input/Output Controller Hu... |

18 |

| <TABLE ROW> |

18 |

| Basic I/O System (BIOS) |

18 |

| Basic I/O System (BIOS) |

18 |

| Based on American Megatrends core, including: |

18 |

| • 4 megabits of flash memory |

18 |

| • 4 megabits of flash memory |

18 |

| • Support for PCI 2.2 specification |

18 |

| • Support for DIMM memory modules |

18 |

| <TABLE ROW> |

18 |

| Firmware - BIOS |

18 |

| Firmware - BIOS |

18 |

| Flash EEPROM: Intel’s firmware hub concept |

18 |

| <TABLE ROW> |

18 |

| Operating System |

18 |

| Operating System |

18 |

| All models come preloaded with Windows 2000 |

18 |

| <TABLE ROW> |

18 |

| Main Memory |

18 |

| Main Memory |

18 |

| Three DIMM sockets that support 128MB and 256MB SDRAM memory modules. |

18 |

| <TABLE ROW> |

19 |

| Mass Storage |

19 |

| Mass Storage |

19 |

| Six shelves, supporting:� |

19 |

| • One front-access, third-height 3 1/2-inch drive (for the flexible disk drive) (1-inch height) |

19 |

| • One front-access, third-height 3 1/2-inch drive (for the flexible disk drive) (1-inch height) |

19 |

| • Three front-access, half-height, 5 1/4-inch drives (1-inch height). |

19 |

| • Two internal 3 1/2-inch hard disk drives (1-inch height) |

19 |

| <TABLE ROW> |

19 |

| SCSI Controller |

19 |

| SCSI Controller |

19 |

| Adaptec Ultra 160 SCSI PCI card. |

19 |

| <TABLE ROW> |

19 |

| IDE Controller |

19 |

| IDE Controller |

19 |

| All models include an integrated Ultra ATA-100 capable controller that supports as many as four I... |

19 |

| <TABLE ROW> |

19 |

| Graphics Controllers |

19 |

| Graphics Controllers |

19 |

| • nVIDIA Quadro2 MXR with TwinView or nVIDIA Quadro2 Pro |

19 |

| • nVIDIA Quadro2 MXR with TwinView or nVIDIA Quadro2 Pro |

19 |

| • nVIDIA Quadro2 MXR with TwinView or nVIDIA Quadro2 Pro |

19 |

| • Matrox Millennium G450-Dual monitor AGP graphics controller with 16MB DDR graphics memory (maxi... |

19 |

| <TABLE ROW> |

19 |

| Accessory Card Slots |

19 |

| Accessory Card Slots |

19 |

| One AGP Universal 4X 32-bit slot supporting 1.5V AGP cards (£25W). |

19 |

| <TABLE ROW> |

19 |

| <TABLE ROW> |

19 |

| LAN (internal) |

19 |

| LAN (internal) |

19 |

| All models come with an internal 10/100TX LAN connector. |

19 |

| <TABLE ROW> |

19 |

| CD-ROM Drive |

19 |

| CD-ROM Drive |

19 |

| Models include either an IDE 48X CD-ROM, CD-RW drive, or DVD drive. |

19 |

| <TABLE ROW> |

19 |

| Audio |

19 |

| Audio |

19 |

| Internal speaker attached to the workstation’s chassis and connected by cable to the system board. |

19 |

| <TABLE ROW> |

20 |

| System Board Connectors |

20 |

| System Board Connectors |

20 |

| • One flexible disk drive connector |

20 |

| • One flexible disk drive connector |

20 |

| • One flexible disk drive connector |

20 |

| • Two ATA-100 capable IDE connectors (they each support up to two IDE devices) |

20 |

| • One CD-IN audio connector |

20 |

| • Internal speaker connector |

20 |

| • Battery socket |

20 |

| • Status panel connector |

20 |

| • Main power supply connector and ATX 12V power connector |

20 |

| • Main chassis fan connector |

20 |

| • Processor fan connector |

20 |

| • Chassis intrusion connector |

20 |

| <TABLE ROW> |

20 |

| Rear Connectors (color coded) |

20 |

| Rear Connectors (color coded) |

20 |

| • Keyboard/Mouse |

20 |

| • Keyboard/Mouse |

20 |

| • Keyboard/Mouse |

20 |

| — HP multi-media keyboard with PS/2 connector |

20 |

| — HP multi-media keyboard with PS/2 connector |

20 |

| — HP enhanced scrolling mouse with PS/2 connector |

20 |

| • 25-pin parallel |

20 |

| — Mode: Centronics or bidirectional modes (ECP/EPP) |

20 |

| — Mode: Centronics or bidirectional modes (ECP/EPP) |

20 |

| — Parallel port: 1 (378h, IRQ 7), 2 (278h, IRQ 5), or Off |

20 |

| • 9-pin serial (two, buffered) |

20 |

| — Standard: Two UART 16550 buffered serial ports (both RS-232-C). |

20 |

| — Standard: Two UART 16550 buffered serial ports (both RS-232-C). |

20 |

| — Serial Ports A and B: 2F8h (IRQ 3), 2E8h (IRQ 3), 3F8h (IRQ 4), 3E8h (IRQ 4), or Off |

20 |

| • Dual USB connectors |

20 |

| • Audio |

20 |

| — LINE IN jack (3.5mm) |

20 |

| — LINE IN jack (3.5mm) |

20 |

| — LINE OUT jack (3.5mm) |

20 |

| — MIC IN jack (3.5mm) |

20 |

| • 10/100TX LAN |

20 |

| <TABLE ROW> |

20 |

| Front Connectors |

20 |

| Front Connectors |

20 |

| • Dual USB connectors |

20 |

| • Dual USB connectors |

20 |

| • Dual USB connectors |

20 |

| • Firewire connector (optionally enabled; see Chapter 5) |

20 |

| packaging |

21 |

| packaging |

21 |

| Figure 1�1 |

21 |

| Figure�1�1 Workstation |

21 |

| Figure�1�1 Workstation |

21 |

| <GRAPHIC> |

22 |

| Figure�1�2 Location of Rear Panel Connectors |

22 |

| <GRAPHIC> |

23 |

| internal features |

23 |

| • Memory Controller Hub (MCH) |

23 |

| • Memory Controller Hub (MCH) |

23 |

| • Input/Output Controller Hub (ICH) |

23 |

| • Host bus |

23 |

| <TABLE> |

23 |

| <TABLE HEADING> |

23 |

| <TABLE ROW> |

23 |

| For information about... |

23 |

| Refer to the chapter... |

23 |

| <TABLE BODY> |

23 |

| <TABLE ROW> |

23 |

| System board components |

23 |

| system board |

23 |

| <TABLE ROW> |

23 |

| HP�BIOS routines |

23 |

| hp BIOS |

23 |

| <TABLE ROW> |

23 |

| Tests and error messages |

23 |

| tests and error messages |

23 |

| <TABLE ROW> |

23 |

| Graphics, network and SCSI devices, and mass storage devices |

23 |

| hardware components |

23 |

| <TABLE ROW> |

23 |

| Accessories Installation and Parts Replacement |

23 |

| removing and replacing hardware parts |

23 |

| <TABLE ROW> |

23 |

| Use or configuration problems |

23 |

| troubleshooting your workstation |

23 |

| <TABLE ROW> |

23 |

| Troubleshooting and Recovery |

23 |

| troubleshooting your workstation |

23 |

| <TABLE ROW> |

23 |

| Contacting support |

23 |

| troubleshooting your workstation |

23 |

| front panel |

24 |

| front panel |

24 |

| • The On/Off LED is green when the power is on, or the power button is pushed in. If the power is... |

24 |

| • The On/Off LED is green when the power is on, or the power button is pushed in. If the power is... |

24 |

| • The hard disk drive activity LED is orange during POST and hard disk drive access. When the sys... |

24 |

| • The hard disk drive activity LED is orange during POST and hard disk drive access. When the sys... |

24 |

| Figure�1�3 Front Panel |

24 |

| Figure�1�3 Front Panel |

24 |

| <GRAPHIC> |

25 |

| specifications and characteristics |

25 |

| physical characteristics |

25 |

| physical characteristics |

25 |

| <TABLE> |

25 |

| <TABLE BODY> |

25 |

| <TABLE ROW> |

25 |

| System Processing Unit |

25 |

| System Processing Unit |

25 |

| <TABLE ROW> |

25 |

| Weight: (Standard configuration as shipped, excluding keyboard and display) |

25 |

| 14.3 kilograms (31.5 pounds) |

25 |

| <TABLE ROW> |

25 |

| Dimensions |

25 |

| 44.2cm max. (D) ¥ 20.6cm (W) ¥ 47.5cm (H) (17.4 inches ¥ 8.1 inches ¥ 18.7 inches) |

25 |

| <TABLE ROW> |

25 |

| Footprint |

25 |

| 0.09 square meters (0.98 square feet) |

25 |

| electrical specifications |

26 |

| electrical specifications |

26 |

| <TABLE> |

26 |

| <TABLE HEADING> |

26 |

| <TABLE ROW> |

26 |

| Parameter |

26 |

| Total Rating |

26 |

| Peak (15 secs.) |

26 |

| Maximum per PCI Slots 32-bit |

26 |

| Maximum for AGP Slot |

26 |

| <TABLE ROW> |

26 |

| Standard Connector |

26 |

| <TABLE BODY> |

26 |

| <TABLE ROW> |

26 |

| Input voltage |

26 |

| 100-127 VAC |

26 |

| 200-250 �VAC |

26 |

| — |

26 |

| — |

26 |

| — |

26 |

| <TABLE ROW> |

26 |

| Input current (max) |

26 |

| 7.0 A |

26 |

| 3.5 A |

26 |

| — |

26 |

| — |

26 |

| — |

26 |

| <TABLE ROW> |

26 |

| Input frequency |

26 |

| 50 to 60 Hz |

26 |

| — |

26 |

| — |

26 |

| — |

26 |

| <TABLE ROW> |

26 |

| Available power |

26 |

| 250 W |

26 |

| — |

26 |

| 85W total for PCI slots and AGP slot |

26 |

| <TABLE ROW> |

26 |

| Max current at +12�V |

26 |

| 13 A |

26 |

| — |

26 |

| 0.5 A |

26 |

| 1 A |

26 |

| <TABLE ROW> |

26 |

| Max current at -12�V |

26 |

| –1.2 A |

26 |

| — |

26 |

| 0.1 A |

26 |

| — |

26 |

| <TABLE ROW> |

26 |

| Max current at +3.3V |

26 |

| 16 A |

26 |

| — |

26 |

| 7.6 A |

26 |

| 6 A |

26 |

| <TABLE ROW> |

26 |

| Max current at +5V |

26 |

| 25 A |

26 |

| 31 A |

26 |

| 5 A |

26 |

| 2 A |

26 |

| <TABLE ROW> |

26 |

| Max current at -5V |

26 |

| 0.3 A |

26 |

| — |

26 |

| — |

26 |

| — |

26 |

| <TABLE ROW> |

26 |

| Max current at +5V stdby |

26 |

| 2 A |

26 |

| — |

26 |

| — |

26 |

| 1. Disconnect the power cord. |

26 |

| 1. Disconnect the power cord. |

26 |

| 2. Determine what caused the overload, and fix the problem. |

26 |

| 3. Reconnect the power cord, and reboot the workstation. |

26 |

| power consumption and cooling |

27 |

| power consumption and cooling |

27 |

| <TABLE> |

27 |

| <TABLE BODY> |

27 |

| <TABLE ROW> |

27 |

| Additional Component |

27 |

| Additional Component |

27 |

| <TABLE ROW> |

27 |

| • Processor |

27 |

| • Processor |

27 |

| • Processor |

27 |

| • SCSI hard disk drive with I/O access |

27 |

| • SCSI hard disk without I/O access (idle) |

27 |

| • PCI card |

27 |

| 50W 23W � ����� 16W ��������10W to 25W� |

27 |

| - 170.6Btu/h - 78.4Btu/h - 54.5Btu/h - 64.1Btu/h to 122.8Btu/h |

27 |

| environmental specifications |

28 |

| environmental specifications |

28 |

| <TABLE> |

28 |

| <TABLE BODY> |

28 |

| <TABLE ROW> |

28 |

| Environmental Specifications (System Processing Unit with Hard Disk) |

28 |

| Environmental Specifications (System Processing Unit with Hard Disk) |

28 |

| <TABLE ROW> |

28 |

| Operating Temperature |

28 |

| +10 �C to +35 �C (+50 �F to +95 �F). |

28 |

| <TABLE ROW> |

28 |

| Storage Temperature |

28 |

| -40 �C to +70�C (-40 �F to +158 �F). |

28 |

| <TABLE ROW> |

28 |

| Over-Temperature Shutdown |

28 |

| +50�C (+122�F) |

28 |

| <TABLE ROW> |

28 |

| Operating Humidity |

28 |

| 15% to 80% (relative). |

28 |

| <TABLE ROW> |

28 |

| Storage Humidity |

28 |

| 8% to 85% (relative).1 |

28 |

| <TABLE ROW> |

28 |

| Acoustic noise emission (ISO 7779): |

28 |

| • Idle |

28 |

| • Idle |

28 |

| • Operating with hard disk access |

28 |

| ���Sound Power |

28 |

| ���Sound Power |

28 |

| LwA <= 4.6 BA |

28 |

| LwA <= 4.6 BA |

28 |

| LwA <= 5.3 BA |

28 |

| <TABLE ROW> |

28 |

| Operating Altitude |

28 |

| 10,000ft (3048m) max |

28 |

| <TABLE ROW> |

28 |

| Storage Altitude |

28 |

| 15,000ft (4600m) max |

28 |

| power saving and ergonometry |

29 |

| power saving and ergonometry |

29 |

| • No sleeping state: Windows NT 4.0 (Full On and Off). |

29 |

| • No sleeping state: Windows NT 4.0 (Full On and Off). |

29 |

| • ACPI: Windows 2000 (Full On, Standby, Hibernate, Off). |

29 |

| <TABLE> |

29 |

| <TABLE BODY> |

29 |

| <TABLE ROW> |

29 |

| Windows 2000 |

29 |

| Windows 2000 |

29 |

| Windows NT 4.0 |

29 |

| Windows NT 4.0 |

29 |

| <TABLE ROW> |

29 |

| A P M |

29 |

| A |

29 |

| P |

29 |

| M |

29 |

| Full On |

29 |

| Full On |

29 |

| Not Supported by Windows 2000 |

29 |

| Supported |

29 |

| <TABLE ROW> |

29 |

| Suspend |

29 |

| Suspend |

29 |

| Not Supported by Windows NT 4.0 |

29 |

| <TABLE ROW> |

29 |

| Off |

29 |

| Off |

29 |

| Supported |

29 |

| <TABLE ROW> |

29 |

| A C P I |

29 |

| A |

29 |

| C |

29 |

| P |

29 |

| I |

29 |

| Standby (S1 or S3) |

29 |

| Standby (S1 or S3) |

29 |

| Supported (implemented as S3, Suspend to RAM) |

29 |

| APM only Operating System |

29 |

| <TABLE ROW> |

29 |

| Hibernate (S4) |

29 |

| Hibernate (S4) |

29 |

| Supported |

29 |

| <TABLE ROW> |

29 |

| Off (S5) |

29 |

| Off (S5) |

29 |

| Supported |

29 |

| power saving and ergonometry for APM systems |

30 |

| power saving and ergonometry for APM systems |

30 |

| <TABLE> |

30 |

| <TABLE HEADING> |

30 |

| <TABLE ROW> |

30 |

| Full On |

30 |

| Suspend |

30 |

| Off |

30 |

| <TABLE BODY> |

30 |

| <TABLE ROW> |

30 |

| Processor |

30 |

| Processor |

30 |

| Normal speed |

30 |

| Halted |

30 |

| Halted |

30 |

| <TABLE ROW> |

30 |

| Display |

30 |

| Display |

30 |

| On |

30 |

| — |

30 |

| — |

30 |

| <TABLE ROW> |

30 |

| Hard disk drive |

30 |

| Hard disk drive |

30 |

| Normal speed |

30 |

| Halted |

30 |

| Halted |

30 |

| <TABLE ROW> |

30 |

| Power consumption |

30 |

| Power consumption |

30 |

| 250W |

30 |

| — |

30 |

| — |

30 |

| <TABLE ROW> |

30 |

| Resume events |

30 |

| Resume events |

30 |

| Keyboard, network (RWU), modem, USB |

30 |

| Space bar or power button, RPO |

30 |

| <TABLE ROW> |

30 |

| Resume delay |

30 |

| Resume delay |

30 |

| A few seconds |

30 |

| Boot delay |

30 |

| power saving modes/resume events for ACPI systems |

31 |

| power saving modes/resume events for ACPI systems |

31 |

| <TABLE> |

31 |

| <TABLE HEADING> |

31 |

| <TABLE ROW> |

31 |

| Full On (S0) |

31 |

| Suspend (S1) |

31 |

| Suspend to RAM (S3) |

31 |

| Suspend to Disk (S4) |

31 |

| Off (S5) |

31 |

| <TABLE BODY> |

31 |

| <TABLE ROW> |

31 |

| Processor |

31 |

| Processor |

31 |

| Normal speed |

31 |

| Halted |

31 |

| Off |

31 |

| Off |

31 |

| Off |

31 |

| <TABLE ROW> |

31 |

| Display |

31 |

| Display |

31 |

| On |

31 |

| Blanked |

31 |

| Off |

31 |

| Off |

31 |

| Off |

31 |

| <TABLE ROW> |

31 |

| Hard Disk Drive |

31 |

| Hard Disk Drive |

31 |

| Normal speed |

31 |

| Halted |

31 |

| Off |

31 |

| Off |

31 |

| Off |

31 |

| <TABLE ROW> |

31 |

| Active Power Planes |

31 |

| Active Power Planes |

31 |

| VCC VCCAux |

31 |

| VCC VCCAux |

31 |

| Memory VCCAux |

31 |

| VCCAux |

31 |

| VCCAux |

31 |

| <TABLE ROW> |

31 |

| Power Consumption |

31 |

| Power Consumption |

31 |

| 250W |

31 |

| — |

31 |

| — |

31 |

| — |

31 |

| — |

31 |

| <TABLE ROW> |

31 |

| Resume Events |

31 |

| Resume Events |

31 |

| Power button, LAN, Modem, USB, Scheduler, HP Start Key |

31 |

| Power button, LAN, Modem, Scheduler, HP Start Key |

31 |

| Power button, LAN, Modem, Scheduler, HP Start Key |

31 |

| Power button, HP Start Key |

31 |

| <TABLE ROW> |

31 |

| Resume Delay |

31 |

| Resume Delay |

31 |

| Instantaneous |

31 |

| Instantaneous |

31 |

| BIOS boot delay |

31 |

| Regular boot delay |

31 |

| power-on from space-bar |

32 |

| power-on from space-bar |

32 |

| • the computer is connected to a Power-On keyboard (recognizable by a Power-On icon on the space ... |

32 |

| • the computer is connected to a Power-On keyboard (recognizable by a Power-On icon on the space ... |

32 |

| • the function hasn’t been disabled by setting switch 6 to |

32 |

| soft power down |

32 |

| soft power down |

32 |

| documentation |

33 |

| documentation |

33 |

| access hp world wide web site |

33 |

| access hp world wide web site |

33 |

| ���http://www.hp.com/workstations/support |

33 |

| where to find the information |

33 |

| where to find the information |

33 |

| 2 system board |

37 |

| 2 system board |

37 |

| • Memory Controller Hub (MCH) |

37 |

| • Memory Controller Hub (MCH) |

37 |

| • Input/Output Controller Hub (ICH2) |

37 |

| • FirmWare Hub (FWH) |

37 |

| • System Bus |

37 |

| system board description |

38 |

| system board description |

38 |

| Figure 2�1 |

38 |

| Figure�2�1 System Board Dimensions |

38 |

| Figure�2�1 System Board Dimensions |

38 |

| <GRAPHIC> |

39 |

| Figure�2�2 System Board Chips and Connectors |

39 |

| Figure�2�2 System Board Chips and Connectors |

39 |

| <GRAPHIC> |

40 |

| architectural view for the x1000 workstation |

40 |

| <GRAPHIC> |

41 |

| accessory board slots |

41 |

| Figure 2�3 |

41 |

| Figure�2�3 Accessory Board Slots |

41 |

| Figure�2�3 Accessory Board Slots |

41 |

| <GRAPHIC> |

41 |

| accelerated graphics port slot |

41 |

| Figure�2�4 AGP Slot |

41 |

| Figure�2�4 AGP Slot |

41 |

| <GRAPHIC> |

42 |

| peripheral component interconnect slots |

43 |

| peripheral component interconnect slots |

43 |

| Figure�2�5 PCI Slots |

43 |

| Figure�2�5 PCI Slots |

43 |

| <GRAPHIC> |

43 |

| • 7W maximum PCI board in the PCI slot |

43 |

| • 15W maximum PCI board in the PCI slot |

43 |

| • 25W� maximum PCI board in the PCI slot |

43 |

| <TABLE> |

44 |

| <TABLE BODY> |

44 |

| <TABLE ROW> |

44 |

| PCI Card |

44 |

| PCI Card |

44 |

| <TABLE ROW> |

44 |

| 3.3V and 5V |

44 |

| 3.3V and 5V |

44 |

| Universal (3.3V or 5V compatible) |

44 |

| Universal (3.3V or 5V compatible) |

44 |

| <TABLE ROW> |

44 |

| PCI Slot |

44 |

| PCI Slot |

44 |

| 32-bit/ 33MHz |

44 |

| 64-bit/ 33MHz |

44 |

| 32-bit/ 33MHz or 66MHz |

44 |

| 64-bit/ 33MHz or 66MHz |

44 |

| <TABLE ROW> |

44 |

| Slots 1, 2, and 3 5V, 32-bit/33MHz |

44 |

| Slots 1, 2, and 3 5V, 32-bit/33MHz |

44 |

| yes |

44 |

| yes |

44 |

| yes |

44 |

| yes |

44 |

| yes |

44 |

| yes |

44 |

| system board switches |

45 |

| system board switches |

45 |

| Figure�2�6 System Board Switches |

45 |

| Figure�2�6 System Board Switches |

45 |

| <GRAPHIC> |

45 |

| <TABLE HEADING> |

45 |

| <TABLE ROW> |

45 |

| Switch |

45 |

| Default Position |

45 |

| Use |

45 |

| <TABLE BODY> |

45 |

| <TABLE ROW> |

45 |

| 1-4 |

45 |

| OFF |

45 |

| Reserved. Do not change default�settings. |

45 |

| <TABLE ROW> |

45 |

| 5 |

45 |

| OFF |

45 |

| Clear CMOS |

45 |

| <TABLE ROW> |

45 |

| 6 |

45 |

| OFF |

45 |

| Clear password |

45 |

| <TABLE ROW> |

45 |

| 7 |

45 |

| OFF |

45 |

| BIOS recovery. ON enables the BIOS recovery mode at next boot. |

45 |

| <TABLE ROW> |

45 |

| 8 |

45 |

| OFF |

45 |

| Reserved. Do not change default settings. |

45 |

| <TABLE ROW> |

45 |

| 9 |

45 |

| OFF |

45 |

| Hardware flash protection. Must be set to ON before any flashing. |

45 |

| <TABLE ROW> |

45 |

| 10 |

45 |

| OFF |

45 |

| Reserved. Do not change default�settings. |

45 |

| chipset |

46 |

| chipset |

46 |

| • The 82845 MCH is a bridge between the: |

46 |

| • The 82845 MCH is a bridge between the: |

46 |

| — System bus |

46 |

| — System bus |

46 |

| — SDRAM bus (main memory) |

46 |

| — AGP 4x (graphic) bus |

46 |

| — Hub link 8-bit |

46 |

| • The 82801BA ICH2 is a bridge between the 32-bit, 33MHz PCI bus and the SMBus. Additionally, the... |

46 |

| — Integrated IDE controller (Ultra ATA/100 capable) |

46 |

| — Integrated IDE controller (Ultra ATA/100 capable) |

46 |

| — Upstream Hub Interface for access to the MCH |

46 |

| — USB controller |

46 |

| — SMBus controller |

46 |

| — Low Pin Count (LPC) interface |

46 |

| — FWH interface |

46 |

| — ACPI Power Management Logic |

46 |

| — AC’97 2.1 Compliant Link |

46 |

| — PCI Interface |

46 |

| — Integrated System Management Controller |

46 |

| — Alert-On-LAN (AOL) |

46 |

| — Integrated LAN Controller |

46 |

| • The Firmware Hub (FWH) stores system BIOS and SCSI BIOS (i.e., the nonvolatile memory component... |

46 |

| memory controller hub (82845) |

47 |

| memory controller hub (82845) |

47 |

| Figure�2�7 MCH Chip Location |

47 |

| Figure�2�7 MCH Chip Location |

47 |

| <GRAPHIC> |

48 |

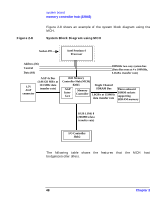

| Figure�2�8 System Block Diagram using MCH |

48 |

| Figure�2�8 System Block Diagram using MCH |

48 |

| <GRAPHIC> |

49 |

| <TABLE HEADING> |

49 |

| <TABLE ROW> |

49 |

| Feature |

49 |

| Feature |

49 |

| <TABLE BODY> |

49 |

| <TABLE ROW> |

49 |

| • Processor/system bus: |

49 |

| • Processor/system bus: |

49 |

| • Processor/system bus: |

49 |

| — Supports a 400MHz system bus |

49 |

| — Supports a 400MHz system bus |

49 |

| — Provides an twelve-deep In-Order Queue that supports as many as eight outstanding transaction r... |

49 |

| — Desktop optimized AGTL+ bus driver technology with integrated AGTL + termination resistors |

49 |

| — Support for 32-bit system bus address |

49 |

| • Accelerated Graphics Port (AGP) interface: |

49 |

| • Accelerated Graphics Port (AGP) interface: |

49 |

| • Accelerated Graphics Port (AGP) interface: |

49 |

| — Single 1.5V AGP connector |

49 |

| — Single 1.5V AGP connector |

49 |

| — AGP 2.0 compliant, including AGP 4x data transfers and 2x/4x Fast Write protocol |

49 |

| — AGP 1.5V connector support with 1.5V signalling only |

49 |

| — AGP PIPE# or SBA initiated accesses to DRAM is not snooped |

49 |

| — AGP FRAME initiated accesses to DRAM are snooped (snooper identifies that data is coherent in c... |

49 |

| — Hierarchical PCI configuration mechanism |

49 |

| — Delayed transaction support for AGP-to-DRAM reads that cannot be serviced immediately |

49 |

| <TABLE ROW> |

49 |

| • Memory Controller |

49 |

| • Memory Controller |

49 |

| • Memory Controller |

49 |

| <TABLE ROW> |

49 |

| — Single Channel SDRAM bus |

49 |

| — Single Channel SDRAM bus |

49 |

| — Single Channel SDRAM bus |

49 |

| — SDRAM 128Mbit and 256Mbit devices |

49 |

| — Supports up to three double sided DIMMs (6 device rows) |

49 |

| — All supported devices must have four banks |

49 |

| — Supports page sizes of 2KB, 4KB, 8KB and 16KB. Page size is individually selected for every row. |

49 |

| — Maximum DRAM address decode space of 4GB |

49 |

| — 128MB to 384MB using 128Mb technology; up to 768MB using 256Mb technology; the 512Mb technology... |

49 |

| — ECC DIMM support |

49 |

| — ECC DIMM support |

49 |

| — ECC DIMM support |

49 |

| — 133MHz SDRAM interface |

49 |

| — 64-bit data interface |

49 |

| — Supports only 3.3V DIMM DRAM configuration |

49 |

| — No registered DIMM support |

49 |

| — Support for Symmetrical and Asymmetrical DRAM addressing |

49 |

| — Refresh Mechanism: CAS-before-RAS only |

49 |

| — Support for DIMM Serial Presence Detect (SPD) scheme via SMBus interface |

49 |

| — STR power management support via self refresh mode using CKE |

49 |

| <TABLE ROW> |

50 |

| • Hub Link 8-bit interface to ICH2: |

50 |

| • Hub Link 8-bit interface to ICH2: |

50 |

| • Hub Link 8-bit interface to ICH2: |

50 |

| — High-speed interconnect between the MCH and ICH2 (266MB/sec) |

50 |

| — High-speed interconnect between the MCH and ICH2 (266MB/sec) |

50 |

| — |

50 |

| <TABLE ROW> |

50 |

| • Power management: |

50 |

| • Power management: |

50 |

| • Power management: |

50 |

| — SMRAM space remapping to A0000h - BFFFFh (128KB). |

50 |

| — SMRAM space remapping to A0000h - BFFFFh (128KB). |

50 |

| — Extended SMRAM space above 256MB, additional 128KB, 256KB, 512KB, 1MB TSEG from top of memory, ... |

50 |

| — ACPI 1.0 compliant power management |

50 |

| — APM 1.2 compliant power management |

50 |

| • Arbitration: |

50 |

| • Arbitration: |

50 |

| • Arbitration: |

50 |

| — Distributed arbitration model for concurrency support |

50 |

| — Distributed arbitration model for concurrency support |

50 |

| — Concurrent operations of system, hub interface, AGP, and memory buses supported through a dedic... |

50 |

| <TABLE ROW> |

50 |

| • 593 FC-BGA MCH package |

50 |

| • 593 FC-BGA MCH package |

50 |

| • 593 FC-BGA MCH package |

50 |

| • I/O device support: |

50 |

| • I/O device support: |

50 |

| • I/O device support: |

50 |

| — I/O Controller Hub (ICH2) |

50 |

| — I/O Controller Hub (ICH2) |

50 |

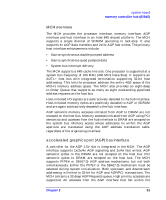

| MCH overview |

51 |

| MCH overview |

51 |

| accelerated graphics port (AGP) bus interface |

51 |

| accelerated graphics port (AGP) bus interface |

51 |

| hub interface |

52 |

| hub interface |

52 |

| SDRAM interface |

52 |

| SDRAM interface |

52 |

| DIMM memory slots |

53 |

| DIMM memory slots |

53 |

| • DIMM1 |

53 |

| • DIMM1 |

53 |

| • DIMM2 |

53 |

| • DIMM3 |

53 |

| Figure�2�9 DIMM Memory Slot |

53 |

| Figure�2�9 DIMM Memory Slot |

53 |

| <GRAPHIC> |

53 |

| read/write buffers |

53 |

| read/write buffers |

53 |

| system clocking |

54 |

| system clocking |

54 |

| the input/output controller hub 2 (82801BA) |

55 |

| the input/output controller hub 2 (82801BA) |

55 |

| Figure�2�10 Input/Output Controller Hub 2 Chip |

55 |

| Figure�2�10 Input/Output Controller Hub 2 Chip |

55 |

| <GRAPHIC> |

56 |

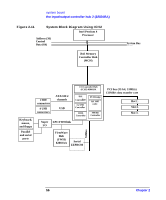

| Figure�2�11 System Block Diagram Using ICH2 |

56 |

| <GRAPHIC> |

57 |

| <TABLE HEADING> |

57 |

| <TABLE ROW> |

57 |

| Feature |

57 |

| Feature |

57 |

| <TABLE BODY> |

57 |

| <TABLE ROW> |

57 |

| • Multifunction PCI bus interface: |

57 |

| • Multifunction PCI bus interface: |

57 |

| • Multifunction PCI bus interface: |

57 |

| — PCI at 32-bit 33MHz |

57 |

| — PCI at 32-bit 33MHz |

57 |

| — PCI 2.2 specification |

57 |

| — 133MB/sec data transfer rate |

57 |

| — Master PCI device support for as many as three devices |

57 |

| • Enhanced DMA controller: |

57 |

| • Enhanced DMA controller: |

57 |

| • Enhanced DMA controller: |

57 |

| — Two 82C37 DMA controllers |

57 |

| — Two 82C37 DMA controllers |

57 |

| — PCI DMA with two PC/PCI channels in pairs |

57 |

| — LPC DMA |

57 |

| — DMA collection buffer to provide Type-F DMA performance for all DMA channels |

57 |

| <TABLE ROW> |

57 |

| • USB, supporting: |

57 |

| • USB, supporting: |

57 |

| • USB, supporting: |

57 |

| — USB 1.1 compliant |

57 |

| — USB 1.1 compliant |

57 |

| — UHCI implementation with four USB ports for serial transfers at 1.2 or 1.5Mbit/sec |

57 |

| — Wake-up from sleeping states |

57 |

| — Legacy keyboard/mouse software |

57 |

| • Interrupt Controller: |

57 |

| • Interrupt Controller: |

57 |

| • Interrupt Controller: |

57 |

| — Two cascaded 82C59 controllers |

57 |

| — Two cascaded 82C59 controllers |

57 |

| — Integrated I/O APIC capability |

57 |

| — 15 interrupt support in 8259 mode, 24 supported in I/O APIC mode |

57 |

| — Serial interrupt protocol |

57 |

| <TABLE ROW> |

57 |

| • Power Management Logic: |

57 |

| • Power Management Logic: |

57 |

| • Power Management Logic: |

57 |

| — ACPI 1.0 compliant |

57 |

| — ACPI 1.0 compliant |

57 |

| — Support for APM-based legacy power management for non-ACPI implementations |

57 |

| — ACPI defined power states (S1, S3, S4, S5) |

57 |

| — ACPI power management timer |

57 |

| — SMI generation |

57 |

| — All registers readable/restorable for proper resume from 0V suspend states |

57 |

| — PCI PME# |

57 |

| • Integrated IDE controller: |

57 |

| • Integrated IDE controller: |

57 |

| • Integrated IDE controller: |

57 |

| — Independent timing of as many as four drives |

57 |

| — Independent timing of as many as four drives |

57 |

| — Ultra ATA/100 mode (100MB/sec) |

57 |

| — Ultra ATA/66 mode (66MB/sec) |

57 |

| — Ultra ATA/33 mode (33MB/sec) |

57 |

| — PIO mode four transfers as fast as 14MB/sec |

57 |

| — Separate IDE connections for primary and secondary cables |

57 |

| — Integrated 16 x 32-bit buffer for IDE PCI burst transfers |

57 |

| — Write ping-pong buffer for faster write performances |

57 |

| <TABLE ROW> |

57 |

| • Real-time clock, supporting: |

57 |

| • Real-time clock, supporting: |

57 |

| • Real-time clock, supporting: |

57 |

| — 256-byte battery-backed CMOS RAM |

57 |

| — 256-byte battery-backed CMOS RAM |

57 |

| — Hardware implementation to indicate century rollover |

57 |

| • System TCO reduction circuits: |

57 |

| • System TCO reduction circuits: |

57 |

| • System TCO reduction circuits: |

57 |

| — Timers to generate SMI# and reset upon |

57 |

| — Timers to generate SMI# and reset upon |

57 |

| — Timers to detect improper processor reset |

57 |

| — Integrated processor frequency strap logic |

57 |

| <TABLE ROW> |

58 |

| • Timers based on 82C54: |

58 |

| • Timers based on 82C54: |

58 |

| • Timers based on 82C54: |

58 |

| — System timer, refresh request, speaker tone output |

58 |

| — System timer, refresh request, speaker tone output |

58 |

| • SMBus |

58 |

| • SMBus |

58 |

| • SMBus |

58 |

| — Host interface allows processor to communicate via SMBus |

58 |

| — Host interface allows processor to communicate via SMBus |

58 |

| — Compatible with two-wire I2C bus |

58 |

| <TABLE ROW> |

58 |

| • System timer, refresh request, speaker tone output |

58 |

| • System timer, refresh request, speaker tone output |

58 |

| • System timer, refresh request, speaker tone output |

58 |

| • GPIO: |

58 |

| • GPIO: |

58 |

| • GPIO: |

58 |

| — TTL, Open-Drain, Inversion |

58 |

| — TTL, Open-Drain, Inversion |

58 |

| <TABLE ROW> |

58 |

| • FWH interface |

58 |

| • FWH interface |

58 |

| • FWH interface |

58 |

| • 3.3V operation with 5V tolerant buffers for IDE and PCI signals |

58 |

| • 3.3V operation with 5V tolerant buffers for IDE and PCI signals |

58 |

| • 3.3V operation with 5V tolerant buffers for IDE and PCI signals |

58 |

| <TABLE ROW> |

58 |

| • 360 pin EBGA package |

58 |

| • 360 pin EBGA package |

58 |

| • 360 pin EBGA package |

58 |

| • Alert-On-LAN (AOL) support |

58 |

| • Alert-On-LAN (AOL) support |

58 |

| • Alert-On-LAN (AOL) support |

58 |

| ICH2 features |

58 |

| ICH2 features |

58 |

| ICH2 architecture |

58 |

| ICH2 architecture |

58 |

| ICH2 PCI bus interface |

59 |

| ICH2 PCI bus interface |

59 |

| SMBus controller |

59 |

| SMBus controller |

59 |

| low pin count interface |

59 |

| low pin count interface |

59 |

| enhanced USB controller |

59 |

| enhanced USB controller |

59 |

| AC’97 controller |

60 |

| AC’97 controller |

60 |

| IDE controller |

60 |

| IDE controller |

60 |

| DMA controller |

60 |

| DMA controller |

60 |

| interrupt controller |

61 |

| interrupt controller |

61 |

| timer/counter block |

61 |

| timer/counter block |

61 |

| advanced programmable interrupt controller |

61 |

| advanced programmable interrupt controller |

61 |

| real time clock |

61 |

| real time clock |

61 |

| • Keeps track of the time |

61 |

| • Keeps track of the time |

61 |

| • Stores system data |

61 |

| enhanced power management |

62 |

| enhanced power management |

62 |

| SoundMAX® Codec (AD1885) |

62 |

| SoundMAX® Codec (AD1885) |

62 |

| • AC’97 2.1 compatibility |

62 |

| • AC’97 2.1 compatibility |

62 |

| • Variable sample rate audio (AC’97 2.1) |

62 |

| • Multiple Codec configuration (AC’97 2.1) |

62 |

| • External audio power-down control (AC’97 2.1) |

62 |

| • Greater than 90 dB |

62 |

| • 16-bit stereo full-duplex Codec |

62 |

| • Four analog line-level stereo inputs for LINE-IN, CD, VIDEO, and AUX |

62 |

| • Two analog line-level mono inputs for speakerphone and PC BEEP |

62 |

| • Mono MIC input w/built-in 20 dB preamp, switchable from two external sources |

62 |

| • High quality CD input with ground sense |

62 |

| • Stereo line-level outputs |

62 |

| • Mono output for speakerphone or internal speaker |

62 |

| • Power management support |

62 |

| • 48-terminal LQFP package |

62 |

| • Full-duplex variable sample rates from 7040Hz to 48kHz with 1Hz resolution |

62 |

| • Up to three Codecs can be chained on a single 5-wire interface |

62 |

| • Jack sense pins provide automatic output switching |

62 |

| • Software-enabled VREFOUT output for microphones and external power amplifier |

63 |

| • Split power supplies (3.3V digital/5V analog) |

63 |

| • Mobile low-power mixer mode |

63 |

| • Extended 6-bit master volume control |

63 |

| • Extended 6-bit headphone volume control |

63 |

| • Digital audio mixer mode |

63 |

| • Phat™ stereo 3D stereo enhancement. |

63 |

| SMBus |

64 |

| SMBus |

64 |

| Figure�2�12 Devices on the SMBus |

64 |

| Figure�2�12 Devices on the SMBus |

64 |

| <GRAPHIC> |

65 |

| ICH2 SMBus master controller |

65 |

| devices on the LPC bus |

65 |

| devices on the LPC bus |

65 |

| Figure 2�13 |

65 |

| Figure�2�13 Devices on the LPC Bus |

65 |

| Figure�2�13 Devices on the LPC Bus |

65 |

| <GRAPHIC> |

66 |

| the super i/o controller |

66 |

| serial/parallel communications ports |

66 |

| serial/parallel communications ports |

66 |

| • Standard mode (PC/XT, PC/AT, and PS/2 compatible). |

66 |

| • Standard mode (PC/XT, PC/AT, and PS/2 compatible). |

66 |

| • Bidirectional mode (PC/XT, PC/AT, and PS/2 compatible). |

66 |

| • Enhanced mode (enhanced parallel port, EPP, compatible). |

66 |

| • High-speed mode (MS/HP extended capabilities port, ECP, compatible). |

66 |

| FDC |

66 |

| FDC |

66 |

| keyboard and mouse controller |

66 |

| keyboard and mouse controller |

66 |

| FirmWare Hub (82802AB) |

67 |

| FirmWare Hub (82802AB) |

67 |

| • Random Number Generator (RNG) |

67 |

| • Random Number Generator (RNG) |

67 |

| • Five General Purpose Inputs (GPI) |

67 |

| • Register-based block locking |

67 |

| • Hardware-based locking |

67 |

| • Enables better protection for the storage and update of system code and data. |

67 |

| • Enables better protection for the storage and update of system code and data. |

67 |

| • Adds flexibility through additional GPIs. |

67 |

| • Allows for quicker introduction of security/manageability features. |

67 |

| <TABLE> |

68 |

| <TABLE HEADING> |

68 |

| <TABLE ROW> |

68 |

| Feature |

68 |

| Feature |

68 |

| <TABLE BODY> |

68 |

| <TABLE ROW> |

68 |

| • Platform compatibility: |

68 |

| • Platform compatibility: |

68 |

| • Platform compatibility: |

68 |

| — Enables security-enhanced platform infrastructure |

68 |

| — Enables security-enhanced platform infrastructure |

68 |

| — Part of the Intel 845 chipset |

68 |

| • Two configurable interfaces: |

68 |

| • Two configurable interfaces: |

68 |

| • Two configurable interfaces: |

68 |

| — FWH interface for system operation |

68 |

| — FWH interface for system operation |

68 |

| — Address/Address Multiplexed (A/A Mux) interface |

68 |

| <TABLE ROW> |

68 |

| • FWH interface mode: |

68 |

| • FWH interface mode: |

68 |

| • FWH interface mode: |

68 |

| — Five signal communication interface supporting 8¥ reads and writes |

68 |

| — Five signal communication interface supporting 8¥ reads and writes |

68 |

| — Register-based read and write protection for each code/data storage blocks |

68 |

| — Hardware write protect pins for the top boot block and the remaining code/data storage blocks |

68 |

| — Five additional GPIs for system design and flexibility |

68 |

| — A hardware RNG |

68 |

| — Integrated Command User Interface (CUI) for requesting access to locking, programming, and eras... |

68 |

| — Operates with 33MHz PCI clock and 3.3V I/O |

68 |

| • Four or eight Mbits of flash memory for system code/data nonvolatile storage: |

68 |

| • Four or eight Mbits of flash memory for system code/data nonvolatile storage: |

68 |

| • Four or eight Mbits of flash memory for system code/data nonvolatile storage: |

68 |

| — Symmetrically blocked, 64KB memory sections |

68 |

| — Symmetrically blocked, 64KB memory sections |

68 |

| — Available in 8-Mbit (Intel® 82802AC) and 4-Mbit (Intel® 82802AB) densities |

68 |

| — Automated byte program and block erase through an integrated Write State Machine (WSM) |

68 |

| <TABLE ROW> |

68 |

| • A/A Mux Interface/Mode, supporting: |

68 |

| • A/A Mux Interface/Mode, supporting: |

68 |

| • A/A Mux Interface/Mode, supporting: |

68 |

| — 11-pin multiplexed address and 8-pin data I/O interface |

68 |

| — 11-pin multiplexed address and 8-pin data I/O interface |

68 |

| — Fast on-board or out-of-system programming |

68 |

| • Power supply specifications: |

68 |

| • Power supply specifications: |

68 |

| • Power supply specifications: |

68 |

| — Vcc: 3.3V +/- 0.3V |

68 |

| — Vcc: 3.3V +/- 0.3V |

68 |

| — Vpp: 3.3V and 12V for fast programming, 80 hours maximum |

68 |

| <TABLE ROW> |

68 |

| • Industry standard package: |

68 |

| • Industry standard package: |

68 |

| • Industry standard package: |

68 |

| — 32L PLCC |

68 |

| — 32L PLCC |

68 |

| • Case temperature operating range |

68 |

| • Case temperature operating range |

68 |

| • Case temperature operating range |

68 |

| • FWH interface |

69 |

| • FWH interface |

69 |

| • A/A Mux interface |

69 |

| system bus |

70 |

| system bus |

70 |

| Figure�2�14 The System Bus |

70 |

| Figure�2�14 The System Bus |

70 |

| <GRAPHIC> |

71 |

| Intel Pentium 4 processor |

71 |

| • Data bus frequency of 400MHz |

71 |

| • Data bus frequency of 400MHz |

71 |

| • Dual independent bus architecture, which combines a dedicated 64-bit Level 2 cache bus (support... |

71 |

| • MMX2 technology, which gives higher performance for media communications, and 3D applications |

71 |

| • Dynamic execution to speed up software performance |

71 |

| • Internet Streaming SIMD Extensions 2 (SSE2) for enhanced floating point and 3D application perf... |

71 |

| • Uses multiple low-power states, such as AutoHALT, Stop-Grant, Sleep, and Deep Sleep to conserve... |

71 |

| processor clock |

71 |

| processor clock |

71 |

| bus frequencies |

71 |

| bus frequencies |

71 |

| voltage regulation module (VRM) |

72 |

| voltage regulation module (VRM) |

72 |

| cache memory |

72 |

| cache memory |

72 |

| • A trace instruction and Level 1 data cache. The trace cache is 4-way set associative. |

72 |

| • A trace instruction and Level 1 data cache. The trace cache is 4-way set associative. |

72 |

| • A 256KB Level 2 cache. The Level 2 cache is 8-way associative. |

72 |

| assigned device interrupts |

73 |

| assigned device interrupts |

73 |

| i/o controller hub interrupts |

73 |

| i/o controller hub interrupts |

73 |

| <TABLE> |

73 |

| <TABLE HEADING> |

73 |

| <TABLE ROW> |

73 |

| Device |

73 |

| Reference Name |

73 |

| REQ/ GNT |

73 |

| Chip-set Interrupt Connection |

73 |

| <TABLE ROW> |

73 |

| INTA |

73 |

| INTB |

73 |

| INTC |

73 |

| INTD |

73 |

| <TABLE BODY> |

73 |

| <TABLE ROW> |

73 |

| AC’97 audio controller |

73 |

| AD1885 |

73 |

| 4 (ICH2) |

73 |

| — |

73 |

| A |

73 |

| — |

73 |

| — |

73 |

| <TABLE ROW> |

73 |

| USB controller |

73 |

| — |

73 |

| — |

73 |

| A |

73 |

| — |

73 |

| — |

73 |

| — |

73 |

| <TABLE ROW> |

73 |

| AGP slot |

73 |

| AGP |

73 |

| — |

73 |

| A |

73 |

| B |

73 |

| — |

73 |

| — |

73 |

| <TABLE ROW> |

73 |

| PCI 32-bit slot #1 |

73 |

| PCI 1 |

73 |

| 0 (ICH2) |

73 |

| F |

73 |

| G |

73 |

| H |

73 |

| E |

73 |

| <TABLE ROW> |

73 |

| PCI 32-bit slot #2 |

73 |

| PCI 2 |

73 |

| 2 (ICH2) |

73 |

| G |

73 |

| H |

73 |

| E |

73 |

| F |

73 |

| <TABLE ROW> |

73 |

| PCI 32-bit slot #3 |

73 |

| PCI 3 |

73 |

| 3 (ICH2) |

73 |

| C |

73 |

| D |

73 |

| A |

73 |

| B |

73 |

| <TABLE ROW> |

73 |

| Extender |

73 |

| 4 (ICH2) |

73 |

| interrupt controllers |

73 |

| interrupt controllers |

73 |

| • PIC mode |

74 |

| • PIC mode |

74 |

| • PIC mode |

74 |

| • Virtual wire mode |

74 |

| • Virtual wire mode |

74 |

| • Symmetric I/O mode |

75 |

| • Symmetric I/O mode |

75 |

| NOTE In PIC mode and virtual wire mode, PCI interrupts are routed to the INT line. In symmetric I... |

75 |

| PCI IRQ lines |

75 |

| PCI IRQ lines |

75 |

| 3 hp BIOS |

77 |

| 3 hp BIOS |

77 |

| overview |

78 |

| overview |

78 |

| • Menu-driven Setup with context-sensitive help. |

78 |

| • Menu-driven Setup with context-sensitive help. |

78 |

| • The address space, with details of the interrupts used. |

78 |

| • POST routines, which are a sequence of tasks the computer performs to ensure that the system is... |

78 |

| • JE – is a two-letter code indicating that it is for the x1000. |

78 |

| • JE – is a two-letter code indicating that it is for the x1000. |

78 |

| • xx – is the major BIOS version. |

78 |

| • yy – is the minor BIOS version. |

78 |

| • z – is an intermediate minor BIOS version. |

78 |

| using the hp setup program |

79 |

| using the hp setup program |

79 |

| main screen |

79 |

| main screen |

79 |

| <TABLE> |

79 |

| <TABLE HEADING> |

79 |

| <TABLE ROW> |

79 |

| �������������� BIOS Setup Utility |

79 |

| <TABLE ROW> |

79 |

| Main |

79 |

| Advanced |

79 |

| Security |

79 |

| Boot |

79 |

| Power |

79 |

| Exit |

79 |

| <TABLE ROW> |

79 |

| �������[��Setup Help��] |

79 |

| <TABLE BODY> |

79 |

| <TABLE ROW> |

79 |

| BIOS Version: |

79 |

| JA.00.13B |

79 |

| . |

79 |

| <TABLE ROW> |

79 |

| <TABLE ROW> |

79 |

| PnP OS |

79 |

| No |

79 |

| <TABLE ROW> |

79 |

| Reset Configuration Data: |

79 |

| No |

79 |

| <TABLE ROW> |

79 |

| <TABLE ROW> |

79 |

| System Time: |

79 |

| 14:42:33 |

79 |

| <TABLE ROW> |

79 |

| System Date: |

79 |

| Oct19 2001 Fri |

79 |

| <TABLE ROW> |

79 |

| <TABLE ROW> |

79 |

| Key Click: |

79 |

| Disabled |

79 |

| <TABLE ROW> |

79 |

| Keyboard auto-repeat rate speed: |

79 |

| 21.8 per Second |

79 |

| <TABLE ROW> |

79 |

| Delay before auto-repeat: |

79 |

| 0.50 per Second |

79 |

| <TABLE ROW> |

79 |

| Numlock at Power-on: |

79 |

| Auto |

79 |

| <TABLE ROW> |

79 |

| Initial Display Mode |

79 |

| Silent |

79 |

| <TABLE ROW> |

79 |

| <TABLE ROW> |

79 |

| F1 |

79 |

| Help |

79 |

| ��� |

79 |

| �����Ø |

79 |

| Select Item |

79 |

| F7/F8 |

79 |

| Change Values |

79 |

| F9 |

79 |

| Setup Defaults |

79 |

| <TABLE ROW> |

79 |

| ESC |

79 |

| Exit |

79 |

| ����¨ |

79 |

| �����Æ |

79 |

| Select Menu |

79 |

| Enter |

79 |

| Select > Submenu |

79 |

| F10 |

79 |

| Previous Values |

79 |

| advanced screen |

80 |

| advanced screen |

80 |

| <TABLE> |

80 |

| <TABLE HEADING> |

80 |

| <TABLE ROW> |

80 |

| Main |

80 |

| Advanced |

80 |

| Security |

80 |

| Boot |

80 |

| Power |

80 |

| Exit |

80 |

| <TABLE ROW> |

80 |

| ��[ Setup Help ] |

80 |

| <TABLE BODY> |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Processors, Memory, and Cache |

80 |

| . |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Floppy Options |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| IDE Device Configuration |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Integrated USB Interface |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Peripheral Configuration |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Integrated Audio Device |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Integrated LAN |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| Video Configuration |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| PCI Device, slot #1 |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| PCI Device, slot #2 |

80 |

| <TABLE ROW> |

80 |

| >> |

80 |

| PCI Device, slot #3 |

80 |

| processors, memory, and cache |

80 |

| processors, memory, and cache |

80 |

| <TABLE> |

80 |

| <TABLE HEADING> |

80 |

| <TABLE ROW> |

80 |

| ����������������������������������������������Advanced |

80 |

| <TABLE ROW> |

80 |

| Processors, Memory, and Cache |

80 |

| ������[ Setup Help ] |

80 |

| <TABLE BODY> |

80 |

| <TABLE ROW> |

80 |

| <TABLE ROW> |

80 |

| Processor Type |

80 |

| Pentium (R) 4 |

80 |

| <TABLE ROW> |

80 |

| CPU Speed |

80 |

| 1700MHz |

80 |

| <TABLE ROW> |

80 |

| CPUID/PATCHID |

80 |

| 0F21/01 |

80 |

| <TABLE ROW> |

80 |

| <TABLE ROW> |

80 |

| Memory Caching |

80 |

| Enabled |

80 |

| <TABLE ROW> |

80 |

| Memory Error Checking |

80 |

| ECC ON |

80 |

| <TABLE ROW> |

80 |

| SDRAM Timing by SPD |

80 |

| Enabled |

80 |

| <TABLE ROW> |

80 |

| ����SDRAM CAS# Latency |

80 |

| 3 Clocks |

80 |

| <TABLE ROW> |

80 |

| �����SDRAM RAS# Latency |

80 |

| 3 Clocks |

80 |

| <TABLE ROW> |

80 |

| ����SDRAM RAS# to CAS# Delay |

80 |

| 3 Clocks |

80 |

| <TABLE ROW> |

80 |

| �����SDRAM Pre-Charge Delay� |

80 |

| 7 Clocks |

80 |

| floppy options |

81 |

| floppy options |

81 |

| <TABLE> |

81 |

| <TABLE HEADING> |

81 |

| <TABLE ROW> |

81 |

| ����Advanced |

81 |

| <TABLE ROW> |

81 |

| Floppy Options |

81 |

| ������[��Setup Help �] |

81 |

| <TABLE BODY> |

81 |

| <TABLE ROW> |

81 |

| <TABLE ROW> |

81 |

| Floppy Disk Controller |

81 |

| Enabled |

81 |

| <TABLE ROW> |

81 |

| Floppy Drive A |

81 |

| 1.44 MB 3.5 |

81 |

| <TABLE ROW> |

81 |

| Floppy Drive B |

81 |

| Not installed |

81 |

| <TABLE ROW> |

81 |

| IDE device configuration |

81 |

| IDE device configuration |

81 |

| <TABLE> |

81 |

| <TABLE HEADING> |

81 |

| <TABLE ROW> |

81 |

| ����Advanced |

81 |

| <TABLE ROW> |

81 |

| IDE Devices Configuration |

81 |

| ���������[ �Setup Help��] |

81 |

| <TABLE BODY> |

81 |

| <TABLE ROW> |

81 |

| <TABLE ROW> |

81 |

| >> |

81 |

| IDE Primary Master |

81 |

| Not Installed |

81 |

| <TABLE ROW> |

81 |

| >> |

81 |

| IDE Primary Slave |

81 |

| Not Installed |

81 |

| <TABLE ROW> |

81 |

| <TABLE ROW> |

81 |

| >> |

81 |

| IDE Secondary Master Device |

81 |

| FX4830T |

81 |

| <TABLE ROW> |

81 |

| >> |

81 |

| IDE Secondary Slave Device |

81 |

| Not Installed |

81 |

| <TABLE ROW> |

81 |

| <TABLE ROW> |

81 |

| >> |

81 |

| Hard Disk Pre-Delay |

81 |

| Disabled |

81 |

| <TABLE ROW> |

81 |

| >> |

81 |

| Integrated Bus IDE adapter |

81 |

| Both Enabled |

81 |

| <TABLE ROW> |

81 |

| IDE primary master device |

81 |

| IDE primary master device |

81 |

| <TABLE> |

81 |

| <TABLE HEADING> |

81 |

| <TABLE ROW> |

81 |

| ����Advanced |

81 |

| <TABLE ROW> |

81 |

| IDE Primary Master Device: |

81 |

| ��������[��Setup Help �] |

81 |

| <TABLE BODY> |

81 |

| <TABLE ROW> |

81 |

| <TABLE ROW> |

81 |

| Type |

81 |

| Auto |

81 |

| <TABLE ROW> |

81 |

| Cylinder |

81 |

| 19166 |

81 |

| <TABLE ROW> |

81 |

| Heads |

81 |

| 16 |

81 |

| <TABLE ROW> |

81 |

| Write Precompensation |

81 |

| <TABLE ROW> |

81 |

| Sectors |

81 |

| 255 |

81 |

| <TABLE ROW> |

81 |

| �����Maximum Capacity |

81 |

| 40037 Mb |

81 |

| <TABLE ROW> |

81 |

| ���LBA Mode |

81 |

| On |

81 |

| <TABLE ROW> |

81 |

| ���Multi-Sector Transfers |

81 |

| Auto |

81 |

| <TABLE ROW> |

81 |

| ���Fast Programmed I/O Modes |

81 |

| 4 |

81 |

| <TABLE ROW> |

81 |

| ���32-Bit Transfer Mode |

81 |

| Off |

81 |

| <TABLE ROW> |

81 |

| ���Ultra DMA Mode |

81 |

| Auto |

81 |

| <TABLE ROW> |

81 |

| integrated USB interface |

82 |

| integrated USB interface |

82 |

| <TABLE> |

82 |

| <TABLE HEADING> |

82 |

| <TABLE ROW> |

82 |

| ����Advanced |

82 |

| <TABLE ROW> |

82 |

| Integrated USB Interface |

82 |

| �����[��Setup Help��] |

82 |

| <TABLE BODY> |

82 |

| <TABLE ROW> |

82 |

| <TABLE ROW> |

82 |

| USB Controller |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| Legacy Keyboard Emulation |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| <TABLE ROW> |

82 |

| peripheral configuration |

82 |

| peripheral configuration |

82 |

| <TABLE> |

82 |

| <TABLE HEADING> |

82 |

| <TABLE ROW> |

82 |

| ����Advanced |

82 |

| <TABLE ROW> |

82 |

| Peripheral Configuration |

82 |

| �������[��Setup Help��] |

82 |

| <TABLE BODY> |

82 |

| <TABLE ROW> |

82 |

| <TABLE ROW> |

82 |

| Parallel Port |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Base I/O Address |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Interrupt |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Parallel Port�Mode |

82 |

| ECP |

82 |

| <TABLE ROW> |

82 |

| On Board Serial PortA |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Base I/O Address |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Interrupt |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| On Board Serial PortB |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Base I/O Address |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| ��Interrupt |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| integrated audio device |

82 |

| integrated audio device |

82 |

| <TABLE> |

82 |

| <TABLE HEADING> |

82 |

| <TABLE ROW> |

82 |

| ����Advanced |

82 |

| <TABLE ROW> |

82 |

| Integrated Audio Device |

82 |

| ��������[���Setup Help��] |

82 |

| <TABLE BODY> |

82 |

| <TABLE ROW> |

82 |

| <TABLE ROW> |

82 |

| Integrated Audio |

82 |

| Auto |

82 |

| <TABLE ROW> |

82 |

| integrated LAN |

83 |

| integrated LAN |

83 |

| <TABLE> |

83 |

| <TABLE HEADING> |

83 |

| <TABLE ROW> |

83 |

| ����Advanced |

83 |

| <TABLE ROW> |

83 |

| Integrated LAN |

83 |

| ��������[ Setup Help ] |

83 |

| <TABLE BODY> |

83 |

| <TABLE ROW> |

83 |

| <TABLE ROW> |

83 |

| Integrated LAN |

83 |

| Auto |

83 |

| <TABLE ROW> |

83 |

| ��MAC address |

83 |

| 00306E1E0305 |

83 |

| <TABLE ROW> |

83 |

| <TABLE ROW> |

83 |

| Option ROM Scan |

83 |

| Enabled |

83 |

| <TABLE ROW> |

83 |

| Bus Master |

83 |

| Disabled |

83 |

| <TABLE ROW> |

83 |

| Bus Latency Timer |

83 |

| 20h |

83 |

| <TABLE ROW> |

83 |

| video configuration |

83 |

| video configuration |

83 |

| <TABLE> |

83 |

| <TABLE HEADING> |

83 |

| <TABLE ROW> |

83 |

| ����Advanced |

83 |

| <TABLE ROW> |

83 |

| Video Configuration |

83 |

| ��������[ Setup Help ] |

83 |

| <TABLE BODY> |

83 |

| <TABLE ROW> |

83 |

| <TABLE ROW> |

83 |

| Graphic Aperture |

83 |

| 64MB |

83 |

| <TABLE ROW> |

83 |

| PCI device, slot #1 |

83 |

| PCI device, slot #1 |

83 |

| <TABLE> |

83 |

| <TABLE HEADING> |

83 |

| <TABLE ROW> |

83 |

| ����Advanced |

83 |

| <TABLE ROW> |

83 |

| PCI Device, Slot 1 |

83 |

| �������[ Setup Help ] |

83 |

| <TABLE BODY> |

83 |

| <TABLE ROW> |

83 |

| <TABLE ROW> |

83 |

| Option ROM Scan |

83 |

| Enabled |

83 |

| <TABLE ROW> |

83 |

| Bus Master |

83 |

| Disabled |

83 |

| <TABLE ROW> |

83 |

| Bus Latency Timer |

83 |

| 20h |

83 |

| <TABLE ROW> |

83 |

| <TABLE ROW> |

83 |

| High Priority |

83 |

| Disabled |

83 |

| security screen |

84 |

| security screen |

84 |

| • systems administrator password |

84 |

| • systems administrator password |

84 |

| • user password |

84 |

| • power-on password |

84 |

| • device start protection |

84 |

| • hardware protection |

84 |

| <TABLE> |

84 |

| <TABLE HEADING> |

84 |

| <TABLE ROW> |

84 |

| Main |

84 |

| Advanced |

84 |

| Security |

84 |

| Boot |

84 |

| Power |

84 |

| Exit |

84 |

| <TABLE ROW> |

84 |

| �����[ Setup Help ] |

84 |

| <TABLE BODY> |

84 |

| <TABLE ROW> |

84 |

| Administrator Password |

84 |

| Clear |

84 |

| . |

84 |

| <TABLE ROW> |

84 |

| ������ |

84 |

| �����Set Administrator Password |

84 |

| [ Enter ] |

84 |

| <TABLE ROW> |

84 |

| User Password |

84 |

| Clear |

84 |

| <TABLE ROW> |

84 |

| ��������Set User Password |

84 |

| [ Enter ] |

84 |

| <TABLE ROW> |

84 |

| ���Power-on Password |

84 |

| Enabled |

84 |

| <TABLE ROW> |

84 |

| >> |

84 |

| Device start Protection |

84 |

| <TABLE ROW> |

84 |

| >> |

84 |

| Hardware Protection |

84 |

| <TABLE ROW> |

84 |

| device start protection |

84 |

| device start protection |

84 |

| <TABLE> |

84 |

| <TABLE HEADING> |

84 |

| <TABLE ROW> |

84 |

| ���� |

84 |

| Security |

84 |

| <TABLE ROW> |

84 |

| Device Start Protection |

84 |

| �����[ Setup Help ] |

84 |

| <TABLE BODY> |

84 |

| <TABLE ROW> |

84 |

| <TABLE ROW> |

84 |

| Start from Network |

84 |

| Enabled |

84 |

| <TABLE ROW> |

84 |

| Start from Floppy |

84 |

| Enabled |

84 |

| <TABLE ROW> |

84 |

| Start from CD-ROM |

84 |

| Enabled |

84 |

| <TABLE ROW> |

84 |

| Start from HDD |

84 |

| Enabled |

84 |

| <TABLE ROW> |

84 |

| Start from USB |

84 |

| Enabled |

84 |

| hardware protection |

85 |

| hardware protection |

85 |

| <TABLE> |

85 |

| <TABLE HEADING> |

85 |

| <TABLE ROW> |

85 |

| ���� |

85 |

| Security |

85 |

| <TABLE ROW> |

85 |

| Hardware Protection |

85 |

| ������[ Setup Help ] |

85 |

| <TABLE BODY> |

85 |

| <TABLE ROW> |

85 |

| <TABLE ROW> |

85 |

| Front USB Ports |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Rear USB Ports |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Flexible Disks |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Write on Floppy Disks |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Hard Disk / CD-ROM |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Hard Disk Boot Sector |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Serial Port A |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Serial Port B |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| Parallel Port |

85 |

| Unlocked |

85 |

| <TABLE ROW> |

85 |

| boot screen |

85 |

| boot screen |

85 |

| • Hard disk drives |

85 |

| • Hard disk drives |

85 |

| • Removable devices |

85 |

| <TABLE> |

85 |

| <TABLE HEADING> |

85 |

| <TABLE ROW> |

85 |

| Main |

85 |

| Advanced |

85 |

| Security |

85 |

| Boot |

85 |

| Power |

85 |

| Exit |

85 |

| <TABLE ROW> |

85 |

| �������[ Setup Help ] |

85 |

| <TABLE BODY> |

85 |

| <TABLE ROW> |

85 |

| Quickboot Mode |

85 |

| Enabled |

85 |

| <TABLE ROW> |

85 |

| Primary Graphics Adapter |

85 |

| AGP |

85 |

| <TABLE ROW> |

85 |

| >> |

85 |

| Boot Device Priority |

85 |

| <TABLE ROW> |

85 |

| power screen |

86 |

| power screen |

86 |

| <TABLE> |

86 |

| <TABLE HEADING> |

86 |

| <TABLE ROW> |

86 |

| Main |

86 |

| Advanced |

86 |

| Security |

86 |

| Boot |

86 |

| Power |

86 |

| Exit |

86 |

| <TABLE ROW> |

86 |

| �����[ Setup Help ] |

86 |

| <TABLE BODY> |

86 |

| <TABLE ROW> |

86 |

| Remote Power On |

86 |

| Enabled |

86 |

| <TABLE ROW> |

86 |

| After Power Failure |

86 |

| Last State |

86 |

| <TABLE ROW> |

86 |

| Boot on LAN after RPO |

86 |

| Enabled |

86 |

| <TABLE ROW> |

86 |

| OPROM display mode |

86 |

| Force BIOS |

86 |

| <TABLE ROW> |

86 |

| exit screen |

86 |

| exit screen |

86 |

| <TABLE> |

86 |

| <TABLE HEADING> |

86 |

| <TABLE ROW> |

86 |