Intel BX80571E5300 Data Sheet - Page 14

Voltage Identification

|

UPC - 735858204996

View all Intel BX80571E5300 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 14 highlights

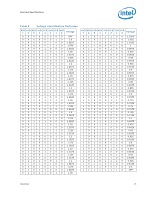

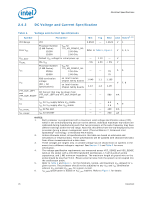

Electrical Specifications 2.2.3 2.3 Note: FSB Decoupling The processor integrates signal termination on the die. In addition, some of the high frequency capacitance required for the FSB is included on the processor package. However, additional high frequency capacitance must be added to the motherboard to properly decouple the return currents from the front side bus. Bulk decoupling must also be provided by the motherboard for proper [A]GTL+ bus operation. Voltage Identification The Voltage Identification (VID) specification for the processor is defined by the Voltage Regulator-Down (VRD) 11.0 Processor Power Delivery Design Guidelines For Desktop LGA775 Socket. The voltage set by the VID signals is the reference VR output voltage to be delivered to the processor VCC lands (see Chapter 2.6.3 for VCC overshoot specifications). Refer to Table 12 for the DC specifications for these signals. Voltages for each processor frequency is provided in Table 4. To support the Deeper Sleep State the platform must use a VRD 11.1 compliant solution. The Deeper Sleep State also requires additional platform support. Individual processor VID values may be calibrated during manufacturing such that two devices at the same core speed may have different default VID settings. This is reflected by the VID Range values provided in Table 4. Refer to the Intel® Pentium® dual-core Processor E5000 Series Specification Update for further details on specific valid core frequency and VID values of the processor. Note that this differs from the VID employed by the processor during a power management event (Thermal Monitor 2, Enhanced Intel SpeedStep® technology, or Extended HALT State). The processor uses eight voltage identification signals, VID[7:0], to support automatic selection of power supply voltages. Table 2 specifies the voltage level corresponding to the state of VID[7:0]. A '1' in this table refers to a high voltage level and a '0' refers to a low voltage level. If the processor socket is empty (VID[7:0] = 11111110), or the voltage regulation circuit cannot supply the voltage that is requested, it must disable itself. The processor provides the ability to operate while transitioning to an adjacent VID and its associated processor core voltage (VCC). This will represent a DC shift in the load line. It should be noted that a low-to-high or high-to-low voltage state change may result in as many VID transitions as necessary to reach the target core voltage. Transitions above the specified VID are not permitted. Table 4 includes VID step sizes and DC shift ranges. Minimum and maximum voltages must be maintained as shown in Table 5, and Figure 1, as measured across the VCC_SENSE and VSS_SENSE lands. The VRM or VRD utilized must be capable of regulating its output to the value defined by the new VID. DC specifications for dynamic VID transitions are included in Table 4 and Table 5 . Refer to the Voltage Regulator Design Guide for further details. 14 Datasheet