Intel BX80571E5300 Data Sheet - Page 46

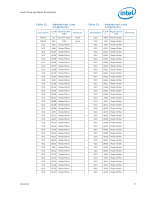

Land Name, Signal Buffer, Direction

|

UPC - 735858204996

View all Intel BX80571E5300 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 46 highlights

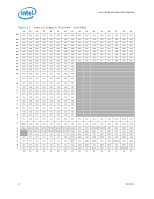

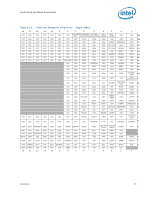

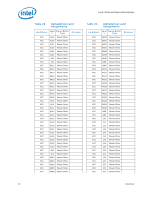

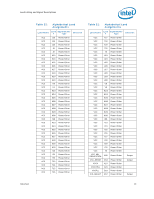

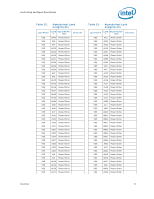

Land Listing and Signal Descriptions Table 22. Alphabetical Land Assignments Land Name Land Signal Buffer # Type Direction FC31 FC32 FC33 FC34 FC35 J16 H15 H16 J17 H4 Power/Other Power/Other Power/Other Power/Other Power/Other FC36 FC37 FC38 FC39 FC40 FC41 FERR#/PBE# GTLREF0 GTLREF1 HIT# HITM# IERR# IGNNE# INIT# ITP_CLK0 ITP_CLK1 LINT0 LINT1 LOCK# MSID0 MSID1 PECI PROCHOT# PSI# PWRGOOD REQ0# REQ1# REQ2# REQ3# REQ4# RESERVED RESERVED RESERVED RESERVED AD3 Power/Other AB3 Power/Other G10 Power/Other AA2 Power/Other AM6 Power/Other C9 Power/Other R3 Asynch CMOS Output H1 Power/Other Input H2 Power/Other Input D4 Common Clock Input/Output E4 Common Clock Input/Output AB2 Asynch CMOS Output N2 Asynch CMOS Input P3 Asynch CMOS Input AK3 TAP Input AJ3 TAP Input K1 Asynch CMOS Input L1 Asynch CMOS Input C3 Common Clock Input/Output W1 Power/Other Output V1 Power/Other Output G5 Power/Other Input/Output AL2 Asynch CMOS Input/Output Y3 Asynch CMOS Output N1 Power/Other Input K4 Source Synch Input/Output J5 Source Synch Input/Output M6 Source Synch Input/Output K6 Source Synch Input/Output J6 Source Synch Input/Output V2 A20 AC4 AE4 Table 22. Alphabetical Land Assignments Land Name Land Signal Buffer # Type Direction RESERVED RESERVED RESERVED RESERVED RESERVED AE6 AH2 D1 D14 D16 RESERVED E23 RESERVED E6 RESERVED E7 RESERVED F23 RESERVED F29 RESERVED G6 RESERVED N4 RESERVED N5 RESERVED P5 RESET# G23 Common Clock RS0# B3 Common Clock RS1# F5 Common Clock RS2# A3 Common Clock SKTOCC# AE8 Power/Other SLP# L2 Asynch CMOS SMI# P2 Asynch CMOS STPCLK# M3 Asynch CMOS TCK AE1 TAP TDI AD1 TAP TDO AF1 TAP TESTHI0 F26 Power/Other TESTHI1 W3 Power/Other TESTHI10 H5 Power/Other TESTHI12/ FC44 W2 Power/Other TESTHI2 F25 Power/Other TESTHI3 G25 Power/Other TESTHI4 G27 Power/Other TESTHI5 G26 Power/Other TESTHI6 G24 Power/Other TESTHI7 F24 Power/Other TESTHI8/FC42 G3 Power/Other TESTHI9/FC43 G4 Power/Other THERMTRIP# M2 Asynch CMOS TMS AC1 TAP Input Input Input Input Output Input Input Input Input Input Output Input Input Input Input Input Input Input Input Input Input Input Input Output Input 46 Datasheet