Intel BX80571E5300 Data Sheet - Page 82

PECI Specifications

|

UPC - 735858204996

View all Intel BX80571E5300 manuals

Add to My Manuals

Save this manual to your list of manuals |

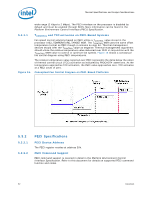

Page 82 highlights

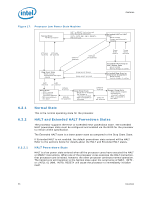

Thermal Specifications and Design Considerations wide range (2 Kbps to 2 Mbps). The PECI interface on the processor is disabled by default and must be enabled through BIOS. More information can be found in the Platform Environment Control Interface (PECI) Specification. 5.3.1.1 Figure 16. TCONTROL and TCC activation on PECI-Based Systems Fan speed control solutions based on PECI utilize a TCONTROL value stored in the processor IA32_TEMPERATURE_TARGET MSR. The TCONTROL MSR uses the same offset temperature format as PECI though it contains no sign bit. Thermal management devices should infer the TCONTROL value as negative. Thermal management algorithms should utilize the relative temperature value delivered over PECI in conjunction with the TCONTROL MSR value to control or optimize fan speeds. Figure 16 shows a conceptual fan control diagram using PECI temperatures. The relative temperature value reported over PECI represents the delta below the onset of thermal control circuit (TCC) activation as indicated by PROCHOT# assertions. As the temperature approaches TCC activation, the PECI value approaches zero. TCC activates at a PECI count of zero. Conceptual Fan Control Diagram on PECI-Based Platforms 5.3.2 5.3.2.1 5.3.2.2 PECI Specifications PECI Device Address The PECI register resides at address 30h. PECI Command Support PECI command support is covered in detail in the Platform Environment Control Interface Specification. Refer to this document for details on supported PECI command function and codes. 82 Datasheet