Intel S1200BT Technical Product Specification - Page 37

Intel, Chipset PCH, I/O Sub-system

|

View all Intel S1200BT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

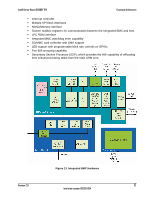

Intel® Server Board S1200BT TPS Functional Architecture For Correctable Errors, there is a certain tolerance observed, since a Correctable Error can be generated by something as random as a stray Cosmic Ray impacting the DIMM. Correctable Errors are counted on a per-DIMM basis, but are just silently recorded until the tolerance threshold is crossed. The Correctable Error Threshold for Intel® Server Board S1200BT board is set at 10 events. When the 10th CE occurs, a single Correctable Error event is logged. 3.3 Intel® Chipset PCH The Intel® C200 Series Chipset is designed for use with Intel® Xeon® E3-1200 Processors, Intel® Xeon® E3-1200 V2 Processors, the 2nd Generation Intel® Core™ i3 Processors or the 3rd Generation Intel® Core™ i3 Processors in a UP server platform. The role of the PCH in the Intel® Server Board S1200BT is to manage the flow of information between its eleven interfaces, described below: DMI interface to Processor PCI Express* Interface PCI Interface Serial ATA Interface LPC Interface to IBMC and TPM USB host interface SMBus Host interface Serial Peripheral interface LAN interface ACPI interface 3.4 I/O Sub-system Intel® C200 Series PCH provides extensive I/O support. 3.4.1 Digital Media Interface (DMI) Direct Media Interface (DMI) is the chip-to-chip connection between the processor and C202 chipset. This high-speed interface integrates advanced priority-based servicing allowing for concurrent traffic and true isochronous transfer capabilities. Base functionality is completely software-transparent, permitting current and legacy software to operate normally. 3.4.2 PCI Express Interface The PCI-E configurations for each SKU are defined below: With Intel® Xeon® E3-1200 Processors or the 2nd Generation Intel® Core™ i3 Processors on S1200BTL One PCI-E x16 Gen2 connector to be used as a x8 link, two PCI-E x8 Gen2 connectors to be used as a x4 link and one SAS module Gen2 connector to be used as a x4 link connected to the PCI-E ports of the processor. One PCI-E x8 Gen2 connector to be used as x4 link connected to the PC-E ports of PCH. With Intel® Xeon® E3-1200 V2 Processors or the 3rd Generation Intel® Core™ i3 Processors on S1200BTL Revision 2.0 25 Intel order number G13326-004