Toshiba Tecra M2-S519 Maintenance Manual - Page 23

Supports DDR266 128MB, 256MB, 512MB and 1GB and DDR333 256MB, 2 System Unit Block Diagram

|

View all Toshiba Tecra M2-S519 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 23 highlights

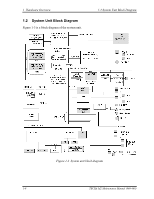

1.2 System Unit Block Diagram 1 Hardware Overview The system unit is composed of the following major components: ‰ Processor • Intel Banias Processor 1.40GHz/1.50GHz/1.60GHz/1.70GHz - Processor core speed:1.40GHz/1.50GHz/1.60GHz/1.70GHz - Processor bus speed: 400MHz - Integrated L1 cache memory: 32KB instruction cache and 32KB write-back data cache, 4-way set associative - Integrated L2 cache memory: 1MB ECC protected cache data array, 8-way set associative - Integrated NDP ‰ Memory Two BTO-compatible memory slots are provided. Expansion up to 2GB (2,048MB) is available. • DDR-SDRAM (Double Data Rate - Synchronous DRAM) • 128MB/256MB/512MB/1GB selectable - 128 MB (16M×16bit×4) - 256 MB (16M×16bit×8) - 512 MB (32M×8bit×16) - 1GB (64M×8bit×16) • 200 pin, SO Dual In-line Memory Modules (SO-DIMM) • 2.5 volt operation • Supports DDR266 (128MB, 256MB, 512MB and 1GB) and DDR333 (256MB, 512MB and 1GB) • Supports PC2100 and PC2700 ‰ Intel Odem (North Bridge) • One Intel RG82855MP is used. • Features: - Banias Processor System Bus Support - DRAM Controller: DDR333/DDR266 Support, 2GB max - Accelerated Graphics Port Interface: adheres to AGP2.0, AGP×4 mode - Hub Link Interface - 593-ball 37.5×37.5 mm FC-BGA package TECRA M2 Maintenance Manual (960-468) 1-9