Fujitsu MHM2150AT Manual/User Guide - Page 187

Transfer of Ultra DMA data, 5.6.3.1 Starting of Ultra DMA data In Burst

|

View all Fujitsu MHM2150AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 187 highlights

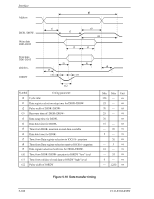

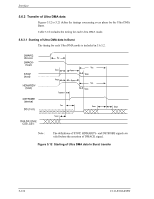

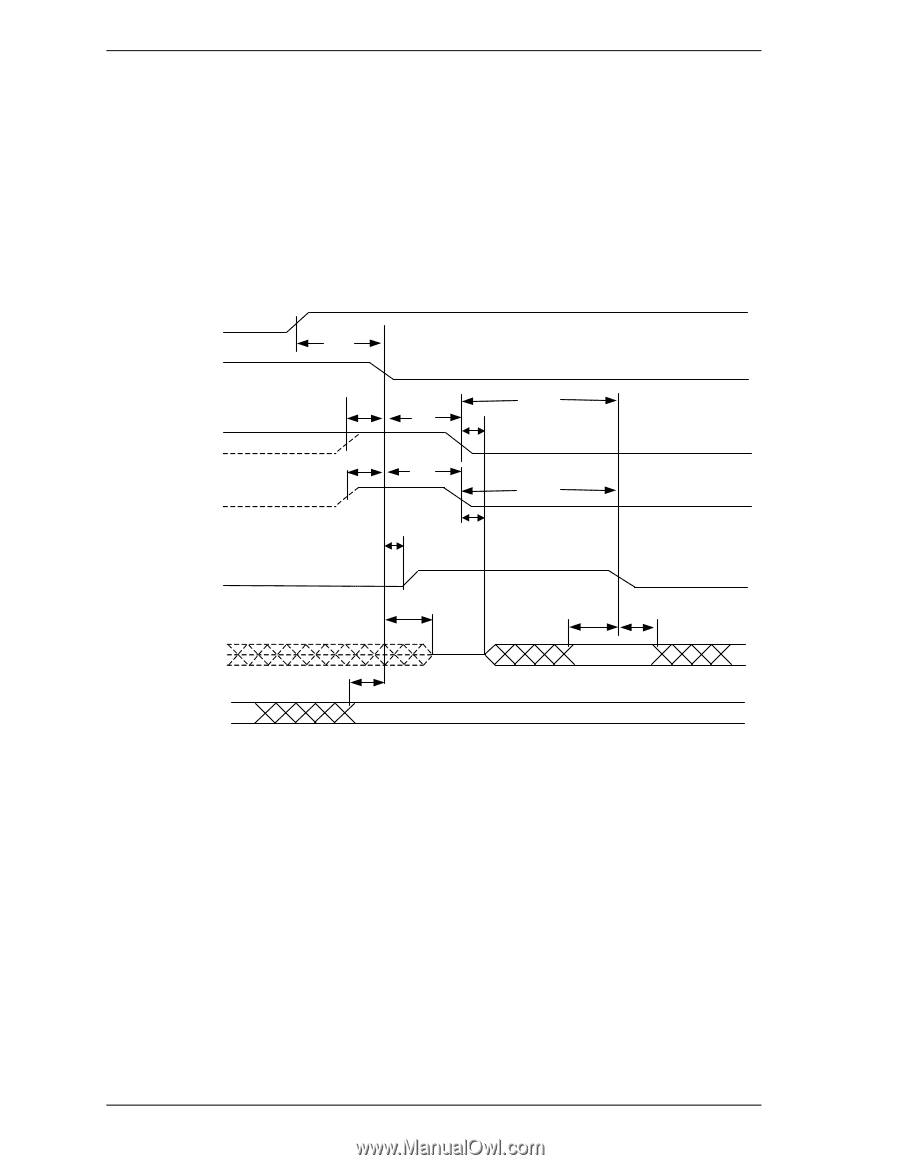

Interface 5.6.3 Transfer of Ultra DMA data Figures 5.12 to 5.21 define the timings concerning every phase for the Ultra DMA Burst. Table 5.18 includes the timing for each Ultra DMA mode. 5.6.3.1 Starting of Ultra DMA data In Burst The timing for each Ultra DMA mode is included in 5.6.3.2. DMARQ (device) DMACK- (host) STOP (host) HDMARDY(host) tUI tACK tACK tENV tENV tZIORDY tFS tZAD tFS tZAD DSTROBE (device) tAZ DD (15:0) tVDS tDVH tACK DA0,DA1,DA2, CS0-,CS1- Note : The definitions of STOP, HDMARDY- and DSTROBE signals are valid before the assertion of DMACK signal. Figure 5.12 Starting of Ultra DMA data In Burst transfer 5-110 C141-E104-03EN

Interface

5-110

C141-E104-03EN

5.6.3

Transfer of Ultra DMA data

Figures 5.12 to 5.21 define the timings concerning every phase for the Ultra DMA

Burst.

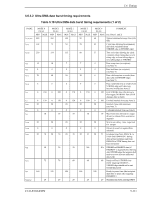

Table 5.18 includes the timing for each Ultra DMA mode.

5.6.3.1

Starting of Ultra DMA data In Burst

The timing for each Ultra DMA mode is included in 5.6.3.2.

Note :

The definitions of STOP, HDMARDY- and DSTROBE signals are

valid before the assertion of DMACK signal.

Figure 5.12

Starting of Ultra DMA data In Burst transfer

DMARQ

(device)

DMACK-

(host)

STOP

(host)

HDMARDY-

(host)

DSTROBE

(device)

DD (15:0)

DA0,DA1,DA2,

CS0-,CS1-

t

UI

t

ENV

t

FS

t

ENV

t

ZAD

t

FS

t

ZAD

t

DVH

t

VDS

t

AZ

t

ZIORDY

t

ACK

t

ACK

t

ACK