Fujitsu MHM2150AT Manual/User Guide - Page 64

Write circuit, Length Limited algorithm.

|

View all Fujitsu MHM2150AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 64 highlights

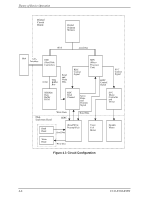

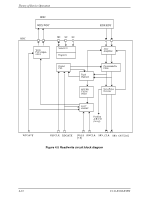

4.6 Read/write Circuit 4.6.2 Write circuit The write data is output from the hard disk controller (HDC) with the NRZ data format, and sent to the encoder circuit in the RDC. The NRZ write data is converted from 16-bit data to 17-bit data by the encoder circuit then sent to the HDIC, and the data is written onto the media. (1) 16/17 MTR MEEPRML This device converts data using the 16/17 MTR (Maximum Transitions Run Length Limited) algorithm. This code is converted so that a maximum of three 1's are placed continuously and so that there are two or fewer 1's in a 17-bit border. (2) Write precompensation Write precompensation compensates, during a write process, for write nonlinearity generated at reading. Table 4.2 shows the write precompensation algorithm. Table 4.2 Write precompensation algorithm Bits 111001 111010 : 111111 000000 000001 : 010000 : 100000 Compensation -7 -6 -1 ±0 +1 +16 +32 C141-E104-03EN 4-11