Fujitsu MHN2150AT Manual/User Guide - Page 185

Ultra DMA CRC rules, For READ DMA or WRITE DMA commands

|

View all Fujitsu MHN2150AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 185 highlights

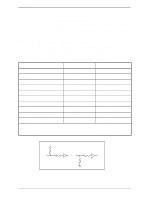

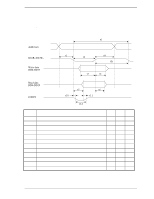

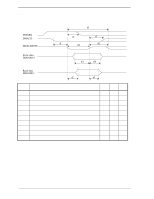

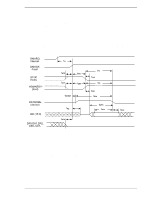

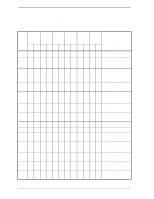

5.5 Ultra DMA Feature Set 13) The host shall neither negate STOP nor HSTROBE until at least tACK after negating DMACK-. 14) The host shall not assert DIOW-, CS0-, CS1-, DA2, DA1, or DA0 until at least tACK after negating DMACK. 5.5.5 Ultra DMA CRC rules The following is a list of rules for calculating CRC, determining if a CRC error has occurred during an Ultra DMA burst, and reporting any error that occurs at the end of a command. a) Both the host and the device shall have a 16-bit CRC calculation function. b) Both the host and the device shall calculate a CRC value for each Ultra DMA burst. c) The CRC function in the host and the device shall be initialized with a seed of 4ABAh at the beginning of an Ultra DMA burst before any data is transferred. d) For each STROBE transition used for data transfer, both the host and the device shall calculate a new CRC value by applying the CRC polynomial to the current value of their individual CRC functions and the word being transferred. CRC is not calculated for the return of STROBE to the asserted state after the Ultra DMA burst termination request has been acknowledged. e) At the end of any Ultra DMA burst the host shall send the results of its CRC calculation function to the device on DD (15:0) with the negation of DMACK-. f) The device shall then compare the CRC data from the host with the calculated value in its own CRC calculation function. If the two values do not match, the device shall save the error and report it at the end of the command. A subsequent Ultra DMA burst for the same command that does not have a CRC error shall not clear an error saved from a previous Ultra DMa burst in the same command. If a miscompare error occurs during one or more Ultra DMA bursts for any one command, at the end of the command, the device shall report the first error that occurred. g) For READ DMA or WRITE DMA commands: When a CRC error is detected, it shall be reported by setting both ICRC and ABRT (bit 7 and bit 2 in the Error register) to one. ICRC is defined as the "Interface CRC Error" bit. The host shall respond to this error by re-issuing the command. h) A host may send extra data words on the last Ultra DMA burst of a data out command. If a device determines that all data has been transferred for a command, the device shall terminate the burst. A device may have already received more data words than were required for the command. These extra words are used by both the host and the device to calculate the CRC, but, on an Ultra DMA data out burst, the extra words shall be discarded by the device. C141-E120-02EN 5-109