Fujitsu MHN2150AT Manual/User Guide - Page 188

Multiword data transfer, Pulse width of DIOR-/DIOW

|

View all Fujitsu MHN2150AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 188 highlights

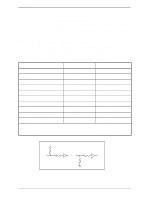

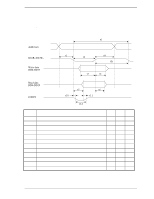

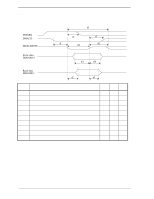

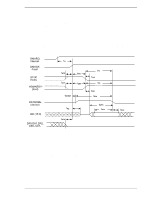

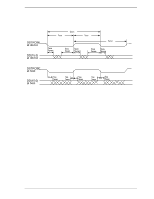

Interface 5.6.2 Multiword data transfer Figure 5.10 shows the multiword DMA data transfer timing between the device and the host system. t0 DMARQ DMACK- DIOR-/DIOW- tC tJ tI tD tK Write data DD0-DD15 tG tH Read data DD0-DD15 tE tF Symbol Timing parameter t0 Cycle time tC Delay time from DMACK assertion to DMARQ negation tD Pulse width of DIOR-/DIOWtE Data setup time for DIORtF Data hold time for DIORtG Data setup time for DIOWtH Data hold time for DIOWtI DMACK setup time for DIOR-/DIOWtJ DMACK hold time for DIOR-/DIOWtK Continuous time of high level for DIOR-/DIOW- Min. Max. Unit 120 - ns - 35 ns 70 - ns - 30 ns 5 - ns 20 - ns 10 - ns 0 - ns 5 - ns 25 - ns Figure 5.10 Multiword DMA data transfer timing (mode 2) 5-112 C141-E120-02EN

Interface

5-112

C141-E120-02EN

5.6.2

Multiword data transfer

Figure 5.10 shows the multiword DMA data transfer timing between the device

and the host system.

tF

tE

tH

tG

tJ

tD

tI

tC

t0

Read data

DD0-DD15

Write data

DD0-DD15

DIOR-/DIOW-

DMACK-

DMARQ

tK

Symbol

Timing parameter

Min.

Max.

Unit

t0

Cycle time

120

—

ns

tC

Delay time from DMACK assertion to DMARQ negation

—

35

ns

tD

Pulse width of DIOR-/DIOW-

70

—

ns

tE

Data setup time for DIOR-

—

30

ns

tF

Data hold time for DIOR-

5

—

ns

tG

Data setup time for DIOW-

20

—

ns

tH

Data hold time for DIOW-

10

—

ns

tI

DMACK setup time for DIOR-/DIOW-

0

—

ns

tJ

DMACK hold time for DIOR-/DIOW-

5

—

ns

tK

Continuous time of high level for DIOR-/DIOW-

25

—

ns

Figure 5.10

Multiword DMA data transfer timing (mode 2)