Fujitsu MHN2150AT Manual/User Guide - Page 189

Ultra DMA data transfer

|

View all Fujitsu MHN2150AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 189 highlights

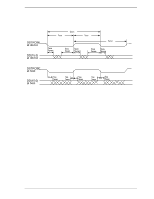

5.6 Timing 5.6.3 Ultra DMA data transfer Figures 5.11 through 5.20 define the timings associated with all phases of Ultra DMA bursts. Table 5.20 contains the values for the timings for each of the Ultra DMA Modes. 5.6.3.1 Initiating an Ultra DMA data in burst 5.6.3.2 contains the values for the timings for each of the Ultra DMA Modes. DMARQ (device) DMACK- (host) STOP (host) HDMARDY(host) DSTROBE (device) DD (15:0) DA0,DA1,DA2, CS0-,CS1- tUI tACK tACK tENV tENV tZIORDY tAZ tACK tFS tZAD tFS tZAD tZFS tDZFS tVDS tDVH Note: The definitions for the STOP, HDMARDY-and DSTROBE signal lines are not in effect until DMARQ and DMACK- are asserted. Figure 5.11 Initiating an Ultra DMA data in burst C141-E120-02EN 5-113

5.6

Timing

C141-E120-02EN

5-113

5.6.3

Ultra DMA data transfer

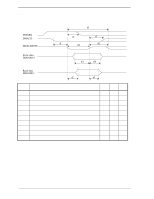

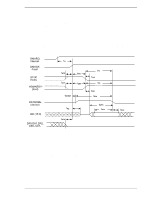

Figures 5.11 through 5.20 define the timings associated with all phases of Ultra

DMA bursts.

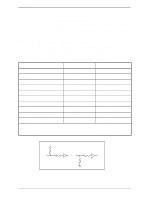

Table 5.20 contains the values for the timings for each of the Ultra DMA Modes.

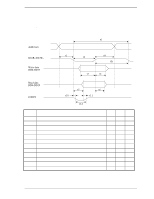

5.6.3.1

Initiating an Ultra DMA data in burst

5.6.3.2 contains the values for the timings for each of the Ultra DMA Modes.

Note:

The definitions for the STOP, HDMARDY-and DSTROBE signal lines are

not in effect until DMARQ and DMACK- are asserted.

Figure 5.11

Initiating an Ultra DMA data in burst

DMARQ

(device)

DMACK-

(host)

STOP

(host)

HDMARDY-

(host)

DSTROBE

(device)

DD (15:0)

DA0,DA1,DA2,

CS0-,CS1-

t

UI

t

ENV

t

FS

t

ENV

t

ZAD

t

FS

t

ZAD

t

DVH

t

AZ

t

ZIORDY

t

ACK

t

ACK

t

ACK

t

VDS

t

DZFS

t

ZFS