Dell PowerEdge R760 Installation and Service Manual - Page 57

Table 50. Processor Settings details continued, Adjacent Cache Line Prefetch

|

View all Dell PowerEdge R760 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 57 highlights

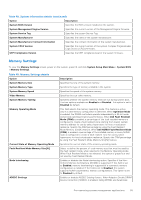

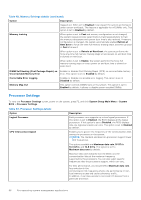

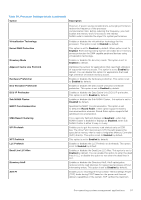

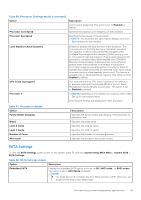

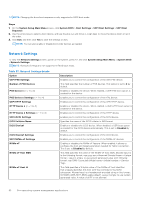

Table 50. Processor Settings details (continued) Option Description However, if power saving considerations outweigh performance, reduce the frequency of the processor communication links. Before reducing the frequency, you must localize the memory and I/O access to the nearest NUMA node to minimize the impact to system performance. Virtualization Technology Kernel DMA Protection Directory Mode Adjacent Cache Line Prefetch Hardware Prefetcher DCU Streamer Prefetcher DCU IP Prefetcher Sub NUMA Cluster MADT Core Enumeration UMA Based Clustering UPI Prefetch XPT Prefetch LLC Prefetch Dead Line LLC Alloc Directory AtoS AVX P1 Enables or disables the virtualization technology for the processor. This option is set to Enabled by default. This option is set to Disabled by default. When option is set to Enabled, BIOS and Operating System will enable direct memory access protection for DMA capable peripheral devices using virtualization technology. Enables or disables the directory mode. This option is set to Enabled by default. Optimizes the system for applications that need high utilization of sequential memory access. This option is set to Enabled by default. You can disable this option for applications that need high utilization of random memory access. Enables or disables the hardware prefetcher. This option is set to Enabled by default. Enables or disables the Data Cache Unit (DCU) streamer prefetcher. This option is set to Enabled by default. Enables or disables the Data Cache Unit (DCU) IP prefetcher. This option is set to Enabled by default. Enables or disables the Sub NUMA Cluster. This option is set to Disabled by default. Specifies the MADT Core Enumeration. This option is set to default in Round Robin. Linear option supports industry core enumeration whereas, Round Robin option supports Dell optimized core enumeration. It is a read-only field and displays as Quadrant , when Sub NUMA Cluster is disabled or displays as Disabled, when Sub NUMA Cluster is either 2-way or 4-way. Enables you to get the memory read started early on DDR bus. The Ultra Path Interconnect (UPI) Rx path spawns the speculative memory that is read to Integrated Memory Controller (iMC) directly. This option is set to Enabled by default. This option is set to Enabled by default. Enables or disables the LLC Prefetch on all threads. This option is set to Enabled by default. Enables or disables the Dead Line LLC Alloc. This option is set to Enabled by default. You can enable this option to enter the dead lines in LLC or disable the option to not enter the dead lines in LLC. Enables or disables the Directory AtoS. AtoS optimization reduces remote read latencies for repeat read accesses without intervening writes. This option is set to Disabled by default. Enables you to reconfigure the processor Thermal Design Power (TDP) levels during POST based on the power and thermal delivery capabilities of the system. TDP verifies the maximum Pre-operating system management applications 57