Foxconn Destroyer English Manual. - Page 50

► RAS to CAS Delay tRCD

|

View all Foxconn Destroyer manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 50 highlights

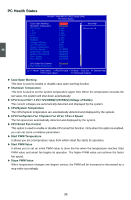

3 rameters, so that the motherboard memory controller (chipset) can better access the memory. This item can be valid only when the "Over Clock Phase Select" is set to [Manual O.C.]. The following items can be valid only when the "DRAM Timing Selectable" is set to [Manual]. ► 1T/2T Memory Timing This item is used for memory timing. 1T/2T timing setup is a memory optimizing technology, it can improve the memory performance by reducing the read delay of memory controller. ► CAS# Latency Time (tCL) The number of memory clocks it takes a DRAM to return data after the read CAS_L is asserted depends on the memory clock frequency. The value that BIOS programs into the memory controller is a function of the target clock frequency. The target clock frequency is determined from the supported CAS latencies at given clock frequencies of each DIMM. ► RAS to CAS Delay (tRCD) This item allows you to select a delay time (in clock cycles) between the CAS and RAS strobe signals. ► Row Precharge Time (tRP) This item allows you to select the DRAM RAS precharge time (in clock cycles). ► Min RAS Active Time (tRAS) This item allows you to set the minimum RAS# active time (in clock cycles). ► Write Recovery Time (tWR) This item allows you to select the write recovery time (in clock cycles). ► Write to Read Delay (tWTR) This item allows you to select a delay time (in clock cycles) between sending the last data from a write operation to the memory and issuing a read command. ► RAS to RAS Delay (tRRD) This item allows you to select a delay time (in clock cycles) between the RAS and RAS strobe signals. ► Read to Precharge (tRTP) Internal READ Command to PRECHARGE Command delay (in clock cycles). ► Row Cycle Time (tRC) This item allows you to set the row cycle time (in clock cycles). tRC = tRAS + tRP. ► Trfc0/1/2/3 for DIMM0/1/2/3 Refresh to Refresh or Refresh to Active command interval. Trfc0: auto-refresh row cycle time for logical DIMM 0. Trfc1: auto-refresh row cycle time for logical DIMM 1. Trfc2: auto-refresh row cycle time for logical DIMM 2. Trfc3: auto-refresh row cycle time for logical DIMM 3. 43