Hitachi IC25N040ATCS04-0 Specifications - Page 83

Drive Address Register, 8 Device/Head Register

|

UPC - 683728198664

View all Hitachi IC25N040ATCS04-0 manuals

Add to My Manuals

Save this manual to your list of manuals |

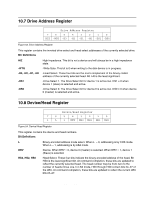

Page 83 highlights

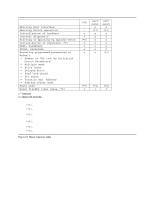

10.7 Drive Address Register Drive Address Register 7 6 5 4 3 2 1 0 HIZ -WTG -H3 -H2 -H1 -H0 -DS1 -DS0 Figure 53. Drive Address Register This register contains the inverted drive select and head select addresses of the currently selected drive. Bit Definitions HIZ -WTG -H3, -H2, -H1, -H0 -DS1 -DS0 High Impedance. This bit is not a device and will always be in a high impedance state. -Write Gate. This bit is 0 when writing to the disk device is in progress. -Head Select. These four bits are the one's complement of the binary coded address of the currently selected head. Bit -H0 is the least significant. -Drive Select 1. The Drive Select bit for device 1 is active low. DS1 = 0 when device 1 (slave) is selected and active. -Drive Select 0. The Drive Select bit for device 0 is active low. DS0 = 0 when device 0 (master) is selected and active. 10.8 Device/Head Register Device/Head Register 7 6 5 4 3 2 1 0 1 L 1 DRV HS3 HS2 HS1 HS0 Figure 54. Device/Head Register This register contains the device and head numbers. Bit Definitions L DRV HS3, HS2, HS0 Binary encoded address mode select. When L = 0, addressing is by CHS mode. When L = 1, addressing is by LBA mode. Device. When DRV = 0, device 0 (master) is selected. When DRV = 1, device 1 (Slave) is selected. Head Select. These four bits indicate the binary encoded address of the head. Bit HS0 is the least significant bit. At command completion, these bits are updated to reflect the currently selected head. The head number may be from zero to the number of heads minus one. In LBA mode, HS3 through HS0 contain bits 24-27 of the LBA. At command completion, these bits are updated to reflect the current LBA bits 24-27. Hitachi Travelstar 60GH & 40GN hard disk drive specifications 70