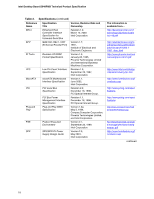

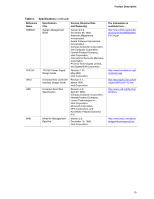

Intel D848PMB Technical Product Specification - Page 23

Intel, 848P Chipset - graphic

|

View all Intel D848PMB manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 23 highlights

Product Description 1.7 Intel® 848P Chipset The Intel 848P chipset consists of the following devices: • Intel 82848P Memory Controller Hub (MCH) with Accelerated Hub Architecture (AHA) bus • Intel 82801EB I/O Controller Hub (ICH5) with AHA bus • Firmware Hub (FWH) The GMCH is a centralized controller for the system bus, the memory bus, and the Accelerated Hub Architecture interface. The ICH5 is a centralized controller for the board's I/O paths. The FWH provides the nonvolatile storage of the BIOS. For information about The Intel 848P chipset Resources used by the chipset Refer to http://developer.intel.com/ Chapter 2 1.7.1 Universal 0.8 V / 1.5 V AGP 3.0 Connector The AGP connector supports the following: • 4x, 8x AGP 3.0 add-in cards with 0.8 V I/O • 1x, 4x AGP 2.0 add-in cards with 1.5 V I/O AGP is a high-performance interface for graphics-intensive applications, such as 3D applications. While based on the PCI Local Bus Specification, Rev. 2.2, AGP is independent of the PCI bus and is intended for exclusive use with graphical display devices. AGP overcomes certain limitations of the PCI bus related to handling large amounts of graphics data with the following features: • Pipelined memory read and write operations that hide memory access latency • Demultiplexing of address and data on the bus for nearly 100 percent efficiency # INTEGRATOR'S NOTES • AGP 2x operation is not supported. • Install memory in the DIMM sockets prior to installing the AGP video card to avoid interference with the memory retention mechanism. • The AGP connector is keyed for Universal 0.8 V AGP 3.0 cards or 1.5 V AGP 2.0 cards only. Do not attempt to install a legacy 3.3 V AGP card. The AGP connector is not mechanically compatible with legacy 3.3 V AGP cards. For information about The location of the AGP connector Obtaining the Accelerated Graphics Port Interface Specification Refer to Figure 1, page 14 Section 1.4, page 17 23