Intel X5365 Design Guide - Page 21

Multiple Core Special Considerations - cpu

|

UPC - 735858199292

View all Intel X5365 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 21 highlights

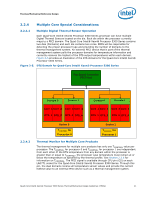

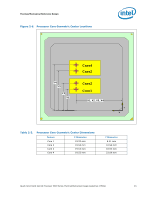

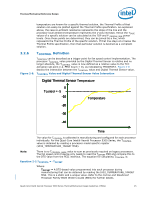

Thermal/Mechanical Reference Design 2.2.4 Multiple Core Special Considerations 2.2.4.1 Multiple Digital Thermal Sensor Operation Each Quad-Core Intel® Xeon® Processor 5300 Series processor can have multiple Digital Thermal Sensors located on the die. Each die within the processor currently maps to a PECI domain. The Quad-Core Intel® Xeon® Processor 5300 Series contains two dies (Domains) and each die contains two cores. BIOS will be responsible for detecting the proper processor type and providing the number of domains to the thermal management system. An external PECI device that is part of the thermal management system polls the processor domains for temperature information and currently receives the highest of the DTS output temperatures within each domain. Figure 2-5 provides an illustration of the DTS domains for the Quad-Core Intel® Xeon® Processor 5300 Series. Figure 2-5. DTS Domain for Quad-Core Intel® Xeon® Processor 5300 Series Fan Speed Controller PECI Host Domain 0 Domain 1 Core_1 Core_2 Core_3 Core_4 DTS_1 DTS_2 DTS_3 DTS_4 Domain 0 Domain 1 Core_1 Core_2 Core_3 Core_4 DTS_1 DTS_2 DTS_3 DTS_4 2.2.4.2 Socket 0 TCONTROL for Processor 0 Socket 1 TCONTROL for Processor 1 Thermal Monitor for Multiple Core Products The thermal management for multiple core products has only one TCONTROL value per processor. The TCONTROL for processor 0 and TCONTROL for processor 1 are independent from each other. If the DTS temperature from any domain within the processor is greater than or equal to TCONTROL, the processor case temperature must remain at or below the temperature as specified by the thermal profile. See Section 2.2.6 for information on TCONTROL. The PECI signal is available through CPU pin (G5) on each LAG771 socket for the Quad-Core Intel® Xeon® Processor 5300 Series. Through this pin, the dual domains receive all temperature sensor values and provide the current hottest value to an external PECI device such as a thermal management system. Quad-Core Intel® Xeon® Processor 5300 Series Thermal/Mechanical Design Guidelines (TMDG) 21