Intel X5365 Design Guide - Page 22

Heatpipe Orientation for Multiple Core Processors, Table 2-2.

|

UPC - 735858199292

View all Intel X5365 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 22 highlights

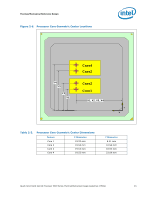

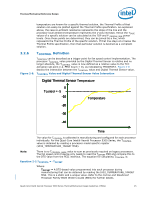

Thermal/Mechanical Reference Design 2.2.4.3 PROCHOT#, THERMTRIP#, and FORCEPR# The PROCHOT# and THERMTRIP# outputs will be shared by all cores on a processor. The first core to reach TCC activation will assert PROCHOT#. A single FORCEPR# input will be shared by every core. Table 2-2 provides an overview of input and output conditions for the Quad-Core Intel® Xeon® Processor 5300 Series thermal management features. Table 2-2. Input and Output Conditions for the Quad-Core Intel® Xeon® Processor 5300 Series Thermal Management Features Item Processor Input Processor Output TM1/TM2 DTSCore X > TCC Activation Temperature All Cores TCC Activation PROCHOT# DTSCore X > TCC Activation Temperature PROCHOT# Asserted THERMTRIP# FORCEPR# DTSCore X > THERMTRIP # Assertion Temperature FORCEPR# Asserted THERMTRIP# Asserted, all cores shut down All Cores TCC Activation Notes: 1. X=1,2,3,4; represents any one of the core1, core2, core3 and core4 in Quad-Core Intel® Xeon® Processor 5300 Series. 2. For more information on PROCHOT#, THERMTRIP#, and FORCEPR# see the Quad-Core Intel® Xeon® Processor 5300 Series Datasheet. 2.2.4.4 Heatpipe Orientation for Multiple Core Processors Thermal management of multiple core processors can be achieved without the use of heatpipe heatsinks, as demonstrated by the Intel Reference Thermal Solution discussed in Section 2.4. To assist customers interested in designing heatpipe heatsinks, processor core locations have been provided. In some cases, this may influence the designer's selection of heatpipe orientation. For this purpose, the core geometric center locations, as illustrated in Figure 2-6, are provided in Table 2-3. Dimensions originate from the vertical edge of the IHS nearest to the pin 1 fiducial as shown in Figure 2-6. 22 Quad-Core Intel® Xeon® Processor 5300 Series Thermal/Mechanical Design Guidelines (TMDG)